# INSTITUT FÜR INFORMATIK

DER LUDWIG-MAXIMILIANS-UNIVERSITÄT MÜNCHEN

Masterarbeit

# Eignungsfeststellung von Flash-Speichern im Automobilbereich

Daniel Haas

## INSTITUT FÜR INFORMATIK

DER LUDWIG-MAXIMILIANS-UNIVERSITÄT MÜNCHEN

#### Masterarbeit

## Eignungsfeststellung von Flash-Speichern im Automobilbereich

Daniel Haas

Aufgabensteller: Prof. Dr. Dieter Kranzlmüller

Betreuer: Dr. Nils gentschen Felde

Jan Schmidt Pascal Jungblut Uwe Henkel (BMW)

Abgabetermin: 6. August 2018

| Hiermit versichere ich, dass ich die vorliegende Masterarbeit selbständig verfasst und zeine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| München, den 4. August 2018                                                                                                                                      |

|                                                                                                                                                                  |

| (Unterschrift des Kandidaten)                                                                                                                                    |

#### Abstract

Die Komplexität der Elektronik in modernen Fahrzeugen wächst stetig an. Damit wachsen auch die Anforderungen der persistenten Datenspeicher in den diversen Steuergeräten an. Für die Auswahl des richtigen persistenten Speichers (meist NAND-Flash) stehen verschiedene Speicherstandards und folglich deren konkrete Implementierungen verschiedener Speicherhersteller zur Verfügung. Diese Speicher gilt es auf ihre Eignung für den Automobilbereich zu testen. Die Eignung wurde in dieser Arbeit als ein Zusammenschluss aus Performance, Effektivität und Funktionsangebot definiert. Für die Eignungsfeststellung wurde eine Testmethodik entwickelt, die auf der Performance Test Specification der Storage Networking Industry Association basiert und durch Anpassungen an den Automobilbereich ergänzt wurde. Anschließend wurde ein Software-Prototyp implementiert und diverse Testreihen an verschiedenen NAND-Flash-Speichern (eMMC und UFS) durchgeführt. Die Ergebnisse zeigten, dass sich Speicher des gleichen Standards und der gleichen Speicherkapazität enorm in ihrer Performance und Effektivität unterscheiden können. Dies ist unter anderem auf die unterschiedliche Strategie der Speicherfirmware zurückzuführen, jedoch auch auf andere Faktoren. Es hat sich also gezeigt, dass die Forschung auf diesem Gebiet durchaus notwendig ist und auch in Zukunft weiter ergänzt werden sollte, um die bestmögliche Applikation im Automobilbereich zu ermöglichen.

## Inhaltsverzeichnis

| 1. | Einle | eitung 5                                       |

|----|-------|------------------------------------------------|

|    | 1.1.  | Ausgangssituation                              |

|    | 1.2.  | Zielsetzung                                    |

|    | 1.3.  | Methodik und Vorgehen                          |

| 2. | Grui  | ndlagen Flash                                  |

|    | 2.1.  | Klassifikation von Halbleiterspeichern         |

|    |       | 2.1.1. Flüchtige Speicher                      |

|    |       | 2.1.2. Nichtflüchtige Speicher                 |

|    | 2.2.  | Flash-Technologie                              |

|    |       | 2.2.1. Aufbau einer Flash-Zelle                |

|    |       | 2.2.2. Architekturen                           |

|    |       | 2.2.3. Lese- und Schreibvorgang                |

|    |       | 2.2.4. Multilevel-Zellen                       |

|    | 2.3.  | Zuverlässigkeit                                |

|    |       | 2.3.1. Data Retention                          |

|    |       | 2.3.2. Read/Program Disturb                    |

|    |       | 2.3.3. Program/Erase Standhaftigkeit           |

|    | 2.4.  | 3-D-Architektur                                |

|    |       | 2.4.1. 2D zu 3D                                |

|    |       | 2.4.2. Grundprinzip                            |

|    |       | 2.4.3. Übersicht Architekturen                 |

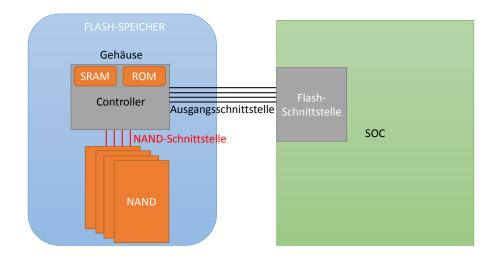

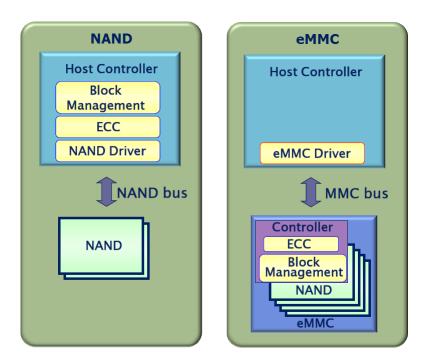

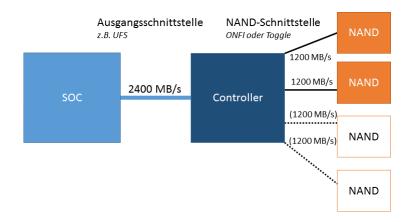

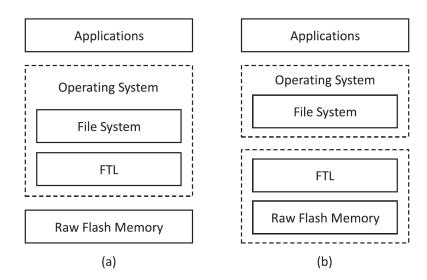

|    | 2.5.  | Systemisches Umfeld des NAND-Speichers         |

|    |       | 2.5.1. Hardwareintegration                     |

|    |       | 2.5.2. Systemische Integration                 |

|    | 2.6.  | Flash-Standardanalyse                          |

|    |       | 2.6.1. Verwendete Speicherschnittstellen       |

|    |       | 2.6.2. Kommunikationsmodell                    |

| 3. | The   | menverwandte Arbeiten 49                       |

|    | 3.1.  | SNIA Performance Test Specification            |

|    |       | 3.1.1. Storage Networking Industry Association |

|    |       | 3.1.2. Solide State Storage                    |

|    |       | 3.1.3. Performance Test Specification(PTS)     |

|    | 3.2.  | Ergänzende Literatur                           |

|    |       | 3.2.1. Write Amplification Factor              |

|    |       | 3.2.2. Temperatur                              |

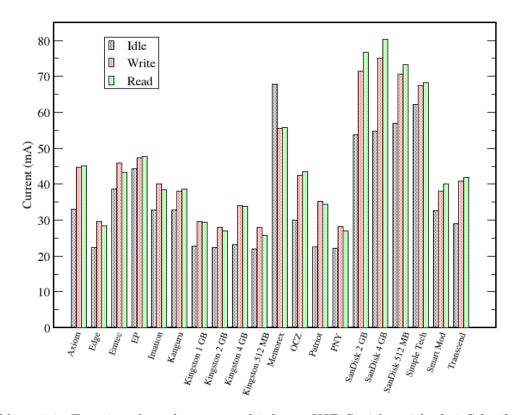

|    |       | 3.2.3. Stromverbrauch                          |

|    |       | 3.2.4. P/E-Cycling und Betriebssystem 61       |

|    | 9.9   | Weiters there enveloped de Anheiters           |

### In halts verzeichn is

|    | 3.4. | Zusammenfassung                            | 67                |

|----|------|--------------------------------------------|-------------------|

| 4. | Mes  | größen und Messmethode                     | 69                |

|    | 4.1. | Diagnose und Konfiguration                 | 69                |

|    |      | 4.1.1. Informationskategorisierung         | 69                |

|    |      | 4.1.2. eMMC                                | 70                |

|    |      | 4.1.3. UFS                                 | 71                |

|    | 4.2. | Messgrößen und Messmethode laut SNIA       | 73                |

|    |      | 4.2.1. Performance Metriken                | 73                |

|    |      | 4.2.2. Workload Parameter                  | 73                |

|    |      | 4.2.3. Testablauf                          | 74                |

|    |      | 4.2.4. Tests                               | 75                |

|    |      | 4.2.5. Testergebnisse                      | 75                |

|    |      | 4.2.6. Testumgebung                        | 76                |

|    | 4.3. | Anpassungen an das automotive Umfeld       | 76                |

|    |      | 4.3.1. Write Amplification Factor          | 76                |

|    |      | 4.3.2. Stromverbrauch                      | 77                |

|    |      | 4.3.3. Temperatur                          | 78                |

|    | 4.4. | Zusammenfassung                            | 78                |

|    |      | 4.4.1. Messgrößen                          | 78                |

|    |      | 4.4.2. Messmethode                         | 79                |

|    |      | 4.4.3. Tests                               | 79                |

|    |      |                                            |                   |

| 5. | Impl | ementierung eines Prototypen               | 83                |

|    | 5.1. | Erstellung eines Input-Datenformats        | 83                |

|    | 5.2. | Spezifikation von Sollzuständen für BMW    | 85                |

|    | 5.3. | Implementierung von Messreihen             | 87                |

|    |      | 5.3.1. Entwicklungsumgebung                | 87                |

|    |      | 5.3.2. Softwarearchitektur                 | 91                |

|    |      | 5.3.3. Implementierung der Testkomponenten | 93                |

|    |      |                                            |                   |

| 6. | Mes  | durchführung                               | 101               |

| 7. | Erge | onisinterpretation und Ausblick            | 105               |

|    | 7.1. | BMW Fallbeispiel                           | 105               |

|    | 7.2. | Benchmark                                  | 107               |

|    |      | 7.2.1. Diagnose                            | 107               |

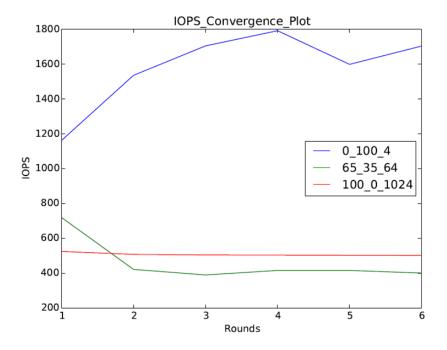

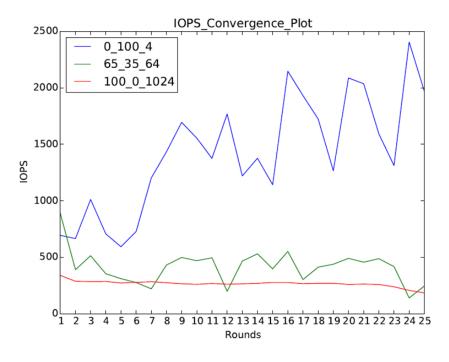

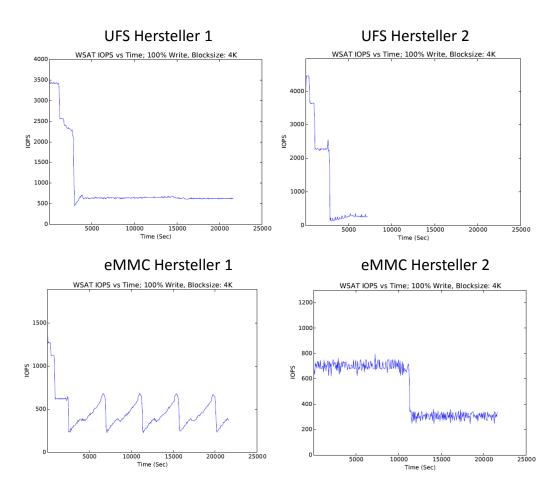

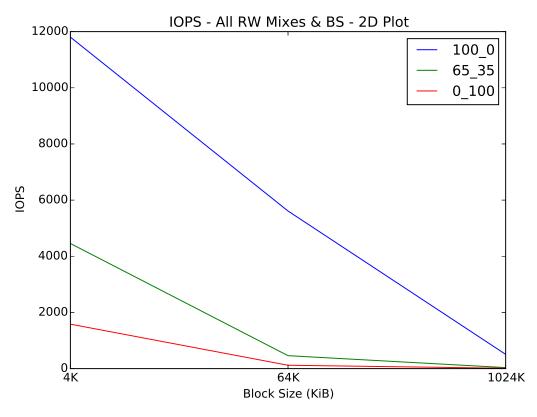

|    |      | 7.2.2. IOPS                                | 107               |

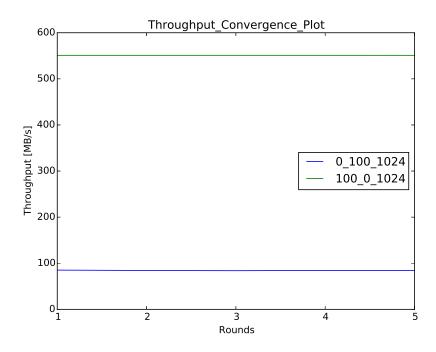

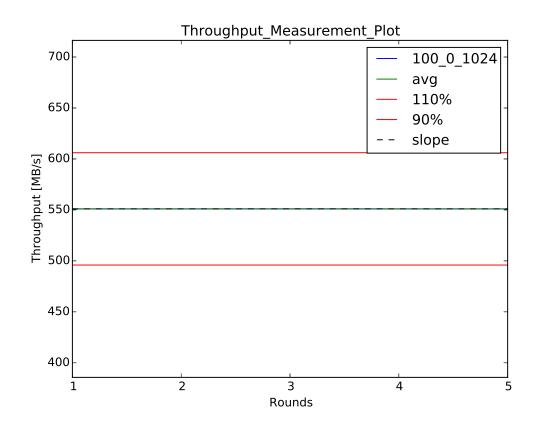

|    |      | 7.2.3. Durchsatz                           | 110               |

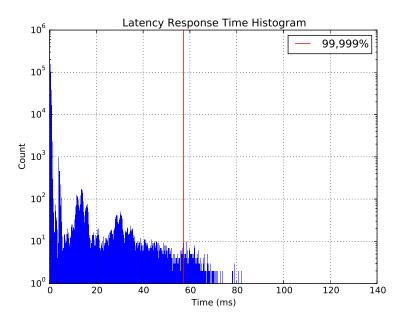

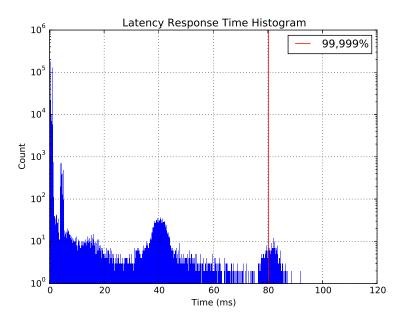

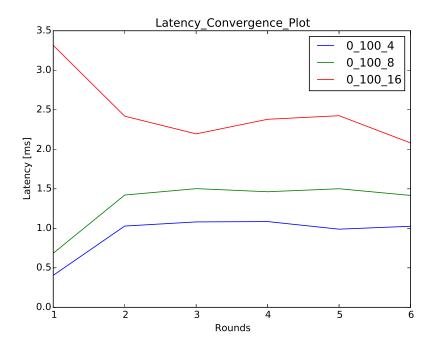

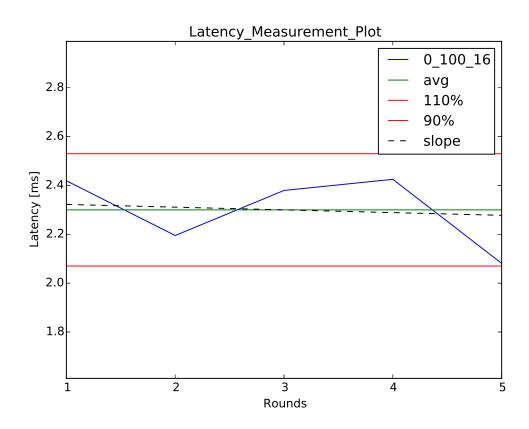

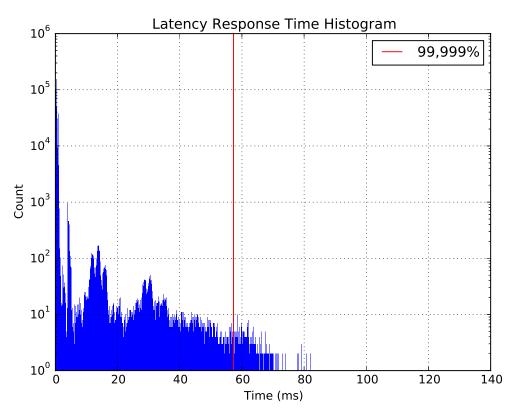

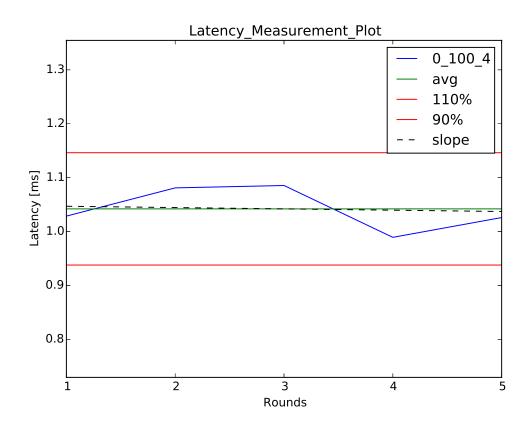

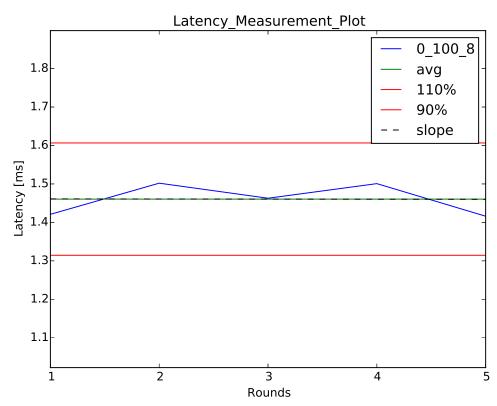

|    |      | 7.2.4. Latenz                              | 111               |

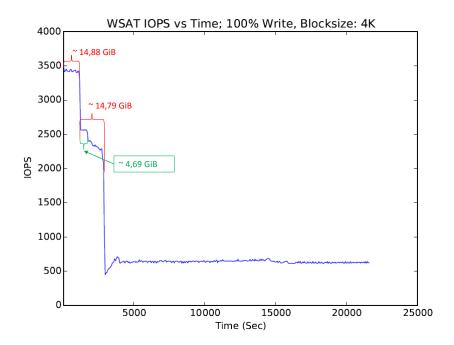

|    |      | 7.2.5. WSAT                                | 112               |

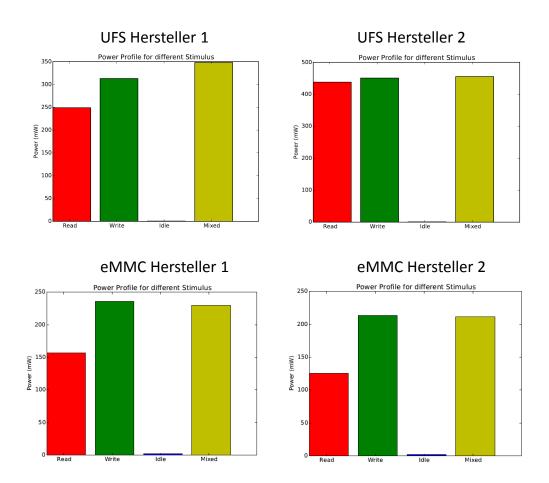

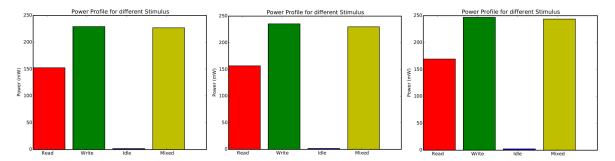

|    |      |                                            | 115               |

|    |      |                                            | 115               |

|    |      |                                            | $\frac{117}{117}$ |

|    | 7.3. | *                                          | 118               |

|    | 7.4. | Ausblick                                   |                   |

|    |      |                                            |                   |

### In halts verzeichn is

| A. Anhang UFS Hersteller 1 Messdaten | 121 |

|--------------------------------------|-----|

| A.1. IOPS                            |     |

| A.2. Latenz                          |     |

| A.3. Durchsatz                       | 129 |

| A.4. Stromtest und WSAT              | 133 |

| A.5. Berichte                        | 133 |

| Abbildungsverzeichnis                | 139 |

| Literaturverzeichnis                 | 143 |

## Abkürzungsverzeichnis

ADAS Advanced Driver Assistance Systems

**HDD** Hard Disk Drive

**OEM** Original Equipment Manufacturer

eMMC embedded Multimedia Card

**UFS** Universal Flash Storage

**DRAM** Dynamic Random Access Memory

**SRAM** Static Random Access Memory

**ROM** Read Only Memory

MOS Metal Oxide Semiconductor Transistor

CMOS Complementary Metal Oxide Semiconductor

XiP Execute in Place

MLC Multi Level Cell

**SLC** Single Level Cell

$\mathbf{TLC} \ \, \mathbf{Triple} \,\, \mathbf{Level} \,\, \mathbf{Cell}$

$\mathbf{QLC}\ \mathrm{Quad}\ \mathrm{Level}\ \mathrm{Cell}$

P/E Program and Erase

**BiCS** Bit Cost Scalable Technology

V-NAND Vertical NAND

CT Charge Trap

CHE Channel-Hot-Electron

FN Fowler-Nordheim

FTL Flash Translation Layer

SoC System-on-a-Chip

ECC Error Correcting Code

#### Inhaltsverzeichnis

**LPN** Logical Page Number

LBN Logical Block Number

LSN Logical Sector Number

LBA Logical Block Adress

OOB Out-Of-Band

**NOP** Number of Partial Programming

**ECN** Erase Count Number

ECB Erase Count Block

FFS Flash File System

API Application Programming Interface

$\mathbf{DBMS} \ \, \mathrm{Datenbank\text{-}Management\text{-}System}$

SNIA Storage Networking Industry Association

SSS Solid State Storage

IOPS Input/Output Operations per Second

**DUT** Device Under Test

**OIO** Outstanding I/O Operations

**FOB** Fresh out of the box

**RW** Read-Write

**BS** Block Size

WAF Write Amplification Factor

JEDEC Joint Electron Device Engineering Council

**OLTP** Online Transaction Processing

PTS Performance Test Specification

ONFI Open NAND Flash Interface

**DDR** Double Data Rate

MIPI Mobile Industry Processor Interface

LU Logical Unit

OCR Operation Conditions Register

CID Device Identification Register

CSD Device Specific Data Register

**EXTCSD** Extended CSD Register

RCA Relative Device Adress Register

$\mathbf{DSR}$  Driver Stage Register

**QSR** Queue Status Register

**RPMB** Replay Protected Memory Block

SCSI Small Computer System Interface

WSAT Write Saturation Test

SS Steady State

UML Unified Modeling Language

XML Extensible Markup Language

JSON JavaScript Object Notation

GUI Graphical User Interface

CLI Command Line Interface

## 1. Einleitung

### 1.1. Ausgangssituation

Der zunehmende informationstechnische Fortschritt im Kraftfahrzeug erleichtert das Leben des Fahrers in vielen Belangen. Die stetige Weiterentwicklung im Bereich Entertainment bringt immer leistungsfähigere Systeme hervor (z. B.Navigation, Sprachassistenz) oder ermöglichen es, den Fond-Passagieren im Fahrzeug beispielsweise einen Film in Blu-Ray-Qualität anzusehen, während sie sich auf dem Weg zu ihrem Ziel befinden. Auch ein großes Thema der Zukunft im Automobilbereich sind die  $Advanced\ Driver\ Assistance\ Systems\ (ADAS)$ , die im Deutschen mit "Fahrassistenzsystem" übersetzt werden können. Dies reicht von kleinen Erleichterungen, wie einem Park-Lenk-Assistenten bis hin zum vollen autonomen Fahren, bei dem das Fahrzeug den Verkehr vollkommen autonom bewältigen kann.

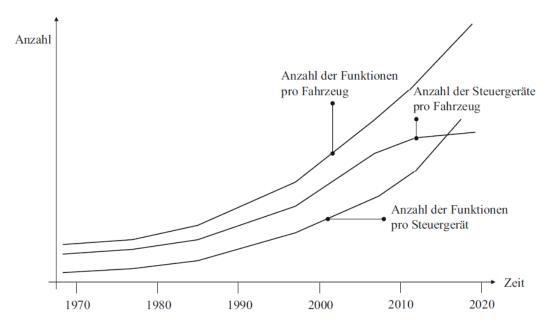

All diese neu entstehenden Funktionen haben eines gemeinsam: Sie werden von einer Vielzahl an zusehend leistungsfähigeren und vernetzten Steuergeräten getrieben. Abbildung 1.1 zeigt, dass die Anzahl der Funktionen pro Fahrzeug auch in Zukunft stark ansteigen wird. Interessant ist, dass sich der Trend zu einer schwächer ansteigenden Anzahl an Steuergeräten jedoch mit mehr Funktionen pro Steuergerät entwickelt. Hier sollen in Zukunft Kosten eingespart werden. Dazu werden bauraumorientiert kleinere funktionsärmere Steuergeräte zu größeren funktionsreicheren Steuergeräten zusammengefasst [SZ16].

Eine logische Konsequenz ist, dass auch die Speichermedien dieser Steuergeräte immer größere Kapazitäten und höhere Leistungsfähigkeit benötigen. Neben Festplatten (*Hard Disk Drive (HDD)*) sind NAND-basierte Flash-Speicher im automotiven Umfeld als Speichermedium sehr verbreitet. Sie können dabei als eingebettete Chips oder als herausnehmbare Speicherkarten implementiert werden [Cou16].

Flash-basierte NAND-Speicher finden ihre Verwendung neben dem Automobilbereich auch im Industrie- und im Konsumbereich, z. B. als Speichermedium in einem Smartphone. Standardisiert werden diese von der Organisation JEDEC Solid State Technology Association. Der JEDEC-Ausschuss entwickelt offene Standards für Halbleiterspeicher. Diese Standards dienen dazu ein Produkt von der Innovation zur Massenware zu transformieren, während Qualität und Zuverlässigkeit aufrecht erhalten werden. Dies führt auf der einen Seite dazu, dass Unternehmen stärker versuchen an innovativen Technologien zu arbeiten und es ermöglicht auf der anderen Seite ein variableres Angebot für den Käufer. Anstatt immer von Grund auf neu mit dem Entwicklungsprozess eines Produktes zu beginnen, können Speicherhersteller ihr Design auf Standards aufbauen und sich gezielter auf neue Innovationen fokussieren <sup>1</sup>.

Solange nicht alle Vorgaben und Spezifikationen eines gewissen Standards erfüllt werden, darf sich ein Produkt nicht JEDEC-konform nennen [JED15]. Daraus resultierend sind diese Standards für Speichertechnologien die Ausgangsbasis dieser Arbeit. In den Standards befinden sich alle wichtigen Vorgaben und vom Speicher zu liefernde Informationen, die schließlich

<sup>&</sup>lt;sup>1</sup>Why JEDEC Standards Matter - https://www.jedec.org/standards-documents/about-jedec-standards Stand 15.01.2018

#### 1. Einleitung

Abbildung 1.1.: Funktionen und Steuergeräte pro Fahrzeug [SZ16]

vom Speicherhersteller komplett implementiert werden müssen. Da der JEDEC-Standard oft verschiedene Varianten eines Speichers enthält (z. B. verschiedene Übertragungsgeschwindigkeiten) und die Hersteller diese und zusätzliche Informationen in ihren Datenblättern preisgeben, gehören auch die Datenblätter zur Ausgangsbasis.

## 1.2. Zielsetzung

Bei Veröffentlichung eines neuen Speicherstandard ist zu prüfen, ob die entwickelten Produkte auch für den Automotive-Bereich geeignet sind, da der JEDEC-Standard kein spezieller Automotive-Standard ist. Ziel der Arbeit ist folglich die Entwicklung einer Methodik und eines Softwarekonzeptes zur Feststellung der Automotive-Eignung neuer Flash-Speichertechnologien. Da es keinen herstellerübergreifenden Automotive-Standard gibt, der alle Anforderungsbereiche eines Datenspeichers definiert, muss die Situation differenzierter betrachtet werden. Für einen speziellen Automobilhersteller, auch oft Original Equipment Manufacturer (OEM) genannt, gelten eigene Standards (bei BMW: Group Standards). Diese befassen sich hauptsächlich mit den Fertigungs-, Qualitätssicherungs- und Qualifizierungsprozessen. Diese werden im Rahmen dieser Arbeit nicht behandelt, da einzelne Tests keine statistisch aussagekräftigen Hinweise über die Qualität eines Produktes liefern.

Bei den Funktionalitätsanforderungen verweisen die Standards darauf, dass die im Lastenheft spezifizierten Anforderungen erfüllt werden müssen. In einem Kraftfahrzeug gibt es, wie schon erwähnt, verschiedene Bereiche, in denen Flash-Speicher verwendet werden. Dazu zählen das Infotainmentsystem<sup>2</sup> oder das ADAS. Diese Bereiche haben zum Teil sehr unterschiedliche Anforderungen (z. B. Temperatur, Performance). Definiert sind diese für einen Bereich in einem speicherspezifischen Lastenheft, welches konkrete Grenzwerte zu verschiede-

<sup>&</sup>lt;sup>2</sup>Zusammenschluss aus Funktionen wie Autoradio, Navigationssystem, Freisprecheinrichtung und weitere Funktionen zu einer zentralen Bedieneinheit

nen Funktionalitäten beinhaltet. Was folglich untersucht werden kann, sind die Eigenschaften (Funktionalitäten) eines Speichers unter verschiedenen Bedingungen. Um nun die Eignung für den Automobilbereich festzustellen, müssen die Eigenschaften eines Speichers für die verschiedenen Lastenhefte eines Automobils validiert werden. Als Ergebnis kann sich somit die Eignung für verschiedene oder für alle Bereiche ergeben. Der Fokus liegt hierbei auf der Erfüllung gewisser Leistungsanforderungen und nicht der Qualitätssicherung. Nicht außer Acht gelassen werden darf, dass diese Eignung für jeden Automobilhersteller unterschiedlich sein kann und somit für jeden Einzelfall separat festgestellt werden muss.

### 1.3. Methodik und Vorgehen

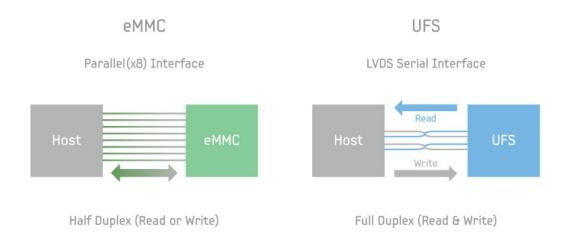

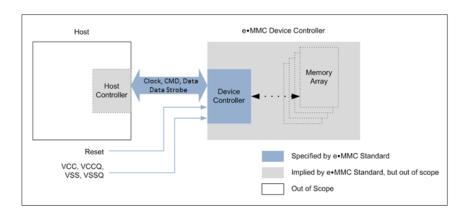

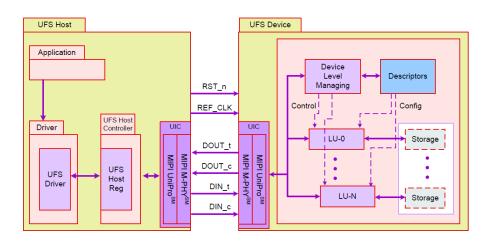

Um eine auf NAND-Flash-Speicher zugeschnittene Testmethode zu entwickeln, sollen in Kapitel 2 die nötigen theoretischen Grundlagen dafür geschaffen werden. Aus jedem Grundlagenunterkapitel soll hervorgehen, wie sich der jeweilige Aspekt auf die Methode auswirken kann. Zuerst wird eine Klassifikation von Halbleiterspeichern vorgenommen, damit der Einsatzbereich des NAND-Speichers besser eingeordnet werden kann. Anschließend werden die wichtigsten technischen Grundlagen zur Flash-Funktionsweise erläutert. Daraus ergibt sich der entscheidende NAND-Performance-Charakter. Darauf folgend sollen die verschiedenen Problemfelder der Zuverlässigkeit dieses Speichertyps und die Auswirkungen auf die Performance untersucht werden. Ein kurzer Einblick in die 3-D-Architektur soll die starken Unterschiede zwischen Speichern des gleichen Standards zeigen und folglich die Notwendigkeit vergleichbare Tests mit verschiedenen Speicher-Technologien durchzuführen. Im nächsten Schritt erfolgt die Einordnung des Flash-Speicherchips in sein systemisches Umfeld, um zu erkennen in welchem Maße dieses Einfluss auf die Funktionalität des Speichers besitzt. Schließlich werden die beiden Flash-Standards embedded Multimedia Card (eMMC) und Universal Flash Storage (UFS) auf ihre Speicherschnittstellen und Kommunikationsmodelle untersucht. Hier können grundlegende Unterschiede in der Konzeption erkannt werden, die auf die Leistung des Speichermediums essenziellen Einfluss haben können.

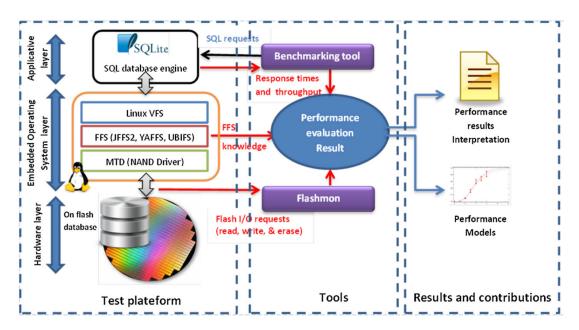

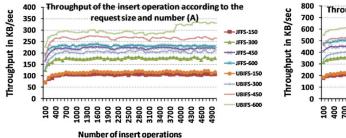

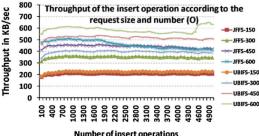

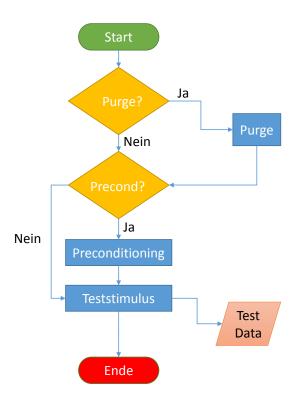

Kapitel 3 zeigt themenverwandte Arbeiten auf. Eine Performance-Testspezifikation der Storage Networking Industry Association (SNIA) wird als Basis der zu erstellenden Testmethode deklariert. Die Spezifikation beinhaltet eine komplette Testmethode für SSD-Speicher. Damit jedoch eingebettete Speicher in kleineren Speichergrößen und mit einem anderen Anforderungsprofil methodisch korrekt getestet werden können, werden dieser Testspezifikation noch Anpassungen auf das automotive Umfeld hinzugefügt. Die Konzepte dafür sollen aus ergänzenden Quellen erarbeitet werden. Schließlich werden noch weitere verwandte Themen gezeigt, die keinen zusätzlichen Aspekte für die eigene Testmethodik enthalten. So können beispielsweise Fehler in deren Herangehensweise analysiert werden und somit für die eigene Methode ausgeschlossen werden.

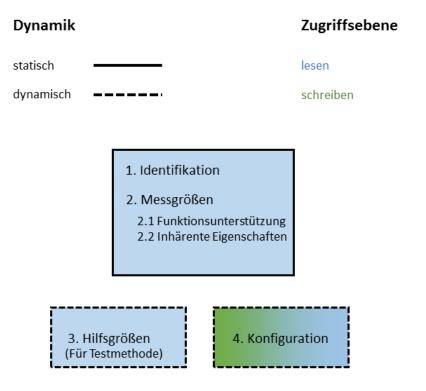

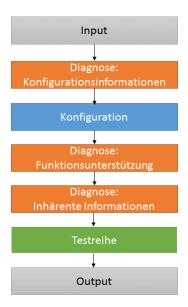

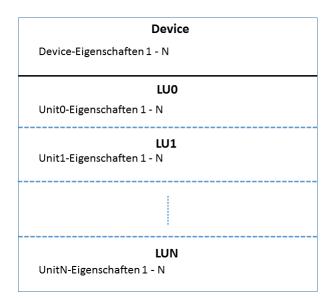

In Kapitel 4 wird das vollständige Testkonzept erarbeitet. Zuerst werden dazu die Informationen, die die beiden Flash-Standards eMMC und UFS zur Verfügung stellen, kategorisiert. Anhand dieser Kategorien wird dann gezeigt, welche Eigenschaften die beiden Standards für die Diagnose und Konfiguration zur Verfügung stellen. Des weiteren werden die bereits erarbeiteten einzelnen relevanten Komponenten der Performance-Testspezifikation der SNIA wiederholt, da diese Basis der eigenen Methode ist. Anschließend werden die konkreten Anpassungen an das automotive Umfeld wiederholt und zusätzliche Tests und Testparameter konzipiert und definiert. In einer darauffolgenden Zusammenfassung werden dann der

#### 1. Einleitung

endgültige Katalog an Messgrößen für beide Speicherstandards und die fertige Messmethode mit konkreten Tests, sowie deren Input und Output festgelegt.

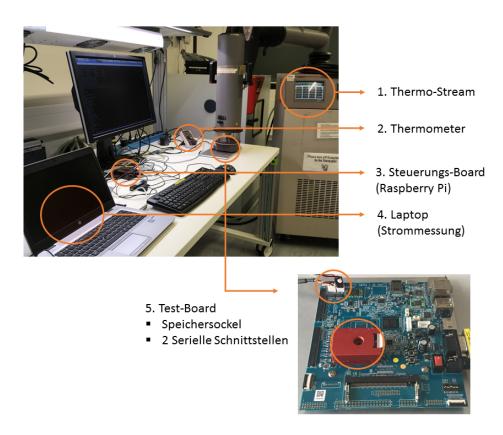

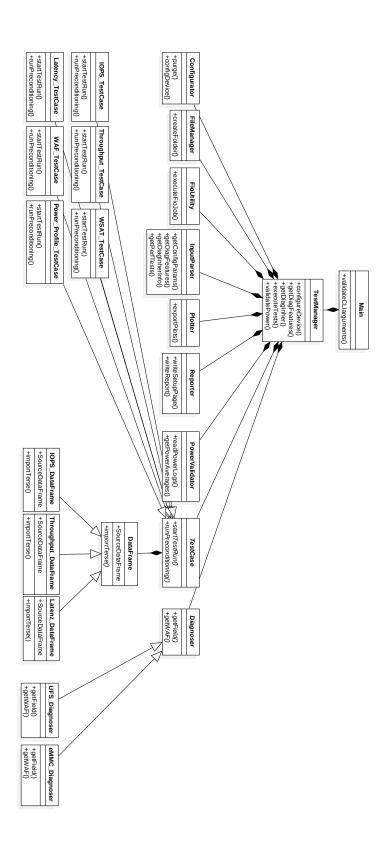

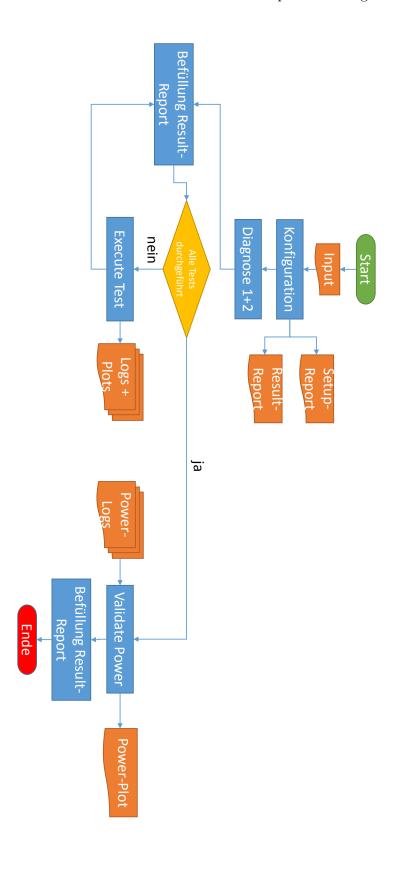

Die anschließende Implementierung eines Prototypen soll in Kapitel 5 beschrieben werden. Erster Schritt hierfür ist die Erstellung eines Datenformates für den Input des Prototypen. Dazu soll ein Standardformat festgelegt werden, das alle Optionen und Metadaten bereitstellt, um ein konkretes Lastenheft darauf umzusetzen. Im Anschluss sollen die Sollzustände für BMW festgelegt werden. Diese ergeben sich aus den konkreten Grenzwerten eines beispielhaften Speicherlastenheftes. Im nächsten Schritt wird die Implementierung der Testsoftware für die in Kapitel 5 konzipierten Messreihen erläutert. Dazu werden die Entwicklungsumgebung bestehend aus Hard- und Softwareumgebung, sowie die entwickelte Softwarearchitektur beleuchtet. Schließlich werden noch die wichtigsten Implementierungsschritte für die einzelnen Testkomponenten aufgezeigt.

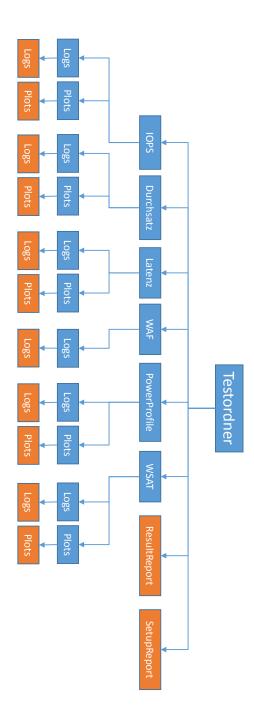

In Kapitel 6 soll die konkrete Durchführung einer kompletten Messreihe für einen UFS-Speicher gezeigt werden. Zunächst wird dafür die konkrete verwendete Input-Datei erläutert. Darauf folgen die notwendigen Schritte, die für die Durchführung einer Testreihe notwendig sind. Anschließend wird noch die Ordnerstruktur des Ergebnisordners beschrieben, der vom Prototypen als Resultat eines Testdurchlaufs erstellt wird.

Schließlich soll in Kapitel 7 eine Ergebnisinterpretation stattfinden. Es werden die Testergebnisse für das BMW-Fallbeispiel und einen Benchmark verschiedener eMMC- und UFS-Speicher analysiert. Beim BMW-Fallbeispiel wird erläutert, warum die abgeprüften Anforderungswerte erfüllt oder nicht erfüllt wurden und was dies an Schlussfolgerungen über die verwendete Testmethode zulässt. Für die Benchmark-Interpretation sollen die Diagnose, alle Einzeltests, sowie der Temperatureinfluss separat diskutiert werden. Erst sollen Auffälligkeiten gefunden und anschließend versucht werden, diese durch das erlangte Wissen über Flash-Speicher zu begründen. In einer anschließenden Zusammenfassung werden die Haupterkenntnisse der Testreihen zusammengefasst und es findet eine Bewertung der eigenen Testmethode statt. Abschließend folgt ein Ausblick auf zukünftige Weiterentwicklungsmöglichkeiten der Testmethode und der daraus resultierende Mehrwert für die Entwicklung von Applikationen im automotiven Umfeld.

## 2. Grundlagen Flash

In diesem Kapitel werden die Grundlagen zu Flash-Speichern erläutert. Aus jedem Unterkapitel geht hervor, welchen Einfluss das jeweilige Thema auf die Performance oder auf die Messmethode hat. Zudem soll das Kapitel dabei helfen, die später im Testprozess erzeugten Ergebnisse auch richtig interpretieren zu können. Anfangs sollen in den Unterkapiteln 2.1 bis 2.2 die physikalischen Eigenschaften des NAND-Flash-Speichers ohne Berücksichtigung des Umfelds (z.B. Controller, Schnittstelle, usw.) analysiert werden. Dadurch soll ein grundlegendes Verständnis für die speziell Flash betreffenden Performancecharakteristika erworben werden. Zu Beginn soll eine grobe Klassifikation von Halbleiterspeichern die Einordnung der Flash-Speicher ermöglichen und ihr Einsatzgebiet zeigen und eingrenzen. Im nächsten Schritts soll der grundsätzliche Aufbau und Funktionsweise einer Flash-Zelle aufgezeigt werden, wobei auf die zwei Flash-Typen NOR und NAND eingegangen wird. Weiter soll das Thema Zuverlässigkeit und mögliche Auswirkungen auf die Performance analysiert werden. Darauf folgt ein tieferer Einblick in den technologischen Fortschritt der NAND-Speichertechnologie. Es handelt sich dabei um einen Wandel von der 2D- zu der 3D-Flash-Architektur. Dem Leser soll ein Eindruck vermittelt werden, welche Hürden bereits zu welchem Preis überwunden wurden und welche Stärken und Schwächen daraus resultieren. In Unterkapitel 2.5 soll das systemische Umfeld im Hinblick auf die Performance und grundlegende Performance-Einflüsse auf den Speicher analysiert werden, die sich durch sein eingebettetes Umfeld und die beteiligten Systemkomponenten ergeben. Eine Analyse der Flash-Standards (eMMC und UFS) auf ihre Speicherschnittstellen und ihre Kommunikationsmodelle soll in Unterkapitel 2.6 grundlegende Unterschiede in der Konzeption zeigen. Daraus können wiederum Schlüsse über die Performance der Speicher gezogen werden.

## 2.1. Klassifikation von Halbleiterspeichern

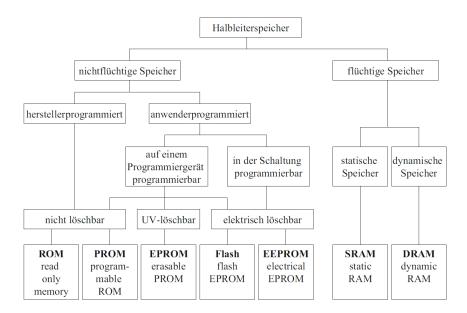

Dieses Unterkapitel soll aufzeigen, welche Arten von Speichermedien grundsätzlich vorhanden sind, wo der NAND-Flash Speicher dabei einzuordnen ist und welches Einsatzgebiet für diese Speicher daraus resultiert. Im Allgemeinen lassen sich Speichermedien in zwei Klassen aufteilen:

- Flüchtige und

- Nichtflüchtige Speicher

Auf Abbildung 2.1 ist eine grobe Übersicht über die etablierten Speichertypen zu sehen.

#### 2.1.1. Flüchtige Speicher

Flüchtige Speicher können ihre Information nur höchstens so lange halten, wie sie mit Spannung versorgt werden (teiweise muss Information sogar kontinuierlich aufgefrischt werden).

Abbildung 2.1.: Übersicht von Speichertechnologien [SZ16]

Wird die Spannungsversorgung entfernt, so verliert der Speicher allmählich seine Informationen. Diese Eigenschaft qualifiziert diese Speicherklasse folglich für spezielle Anwendungsbereiche. So werden diese als Cache (Puffer-Speicher) oder als Arbeitsspeicher verwendet [ARI16].

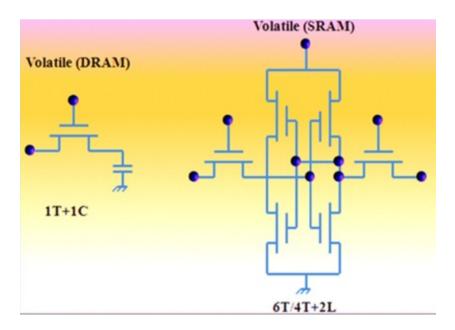

Eine weiteres Unterscheidungskriterium bietet die Einteilung in statische und dynamische Speicher. Der Dynamic Random Access Memory (DRAM), der Vertreter der dynamischen Speicher muss seine Informationen periodisch auffrischen, um die Datenintegrität aufrecht zu erhalten. Dies stellt einen dynamischen Vorgang dar, auf welchen die Namensbebung zurückzuführen ist. Der Static Random Access Memory (SRAM) hingegen muss bei konstanter Spannungsversorgung seine Informationen nicht auffrischen, um seine Datenintegrität zu garantieren. Auf Abbildung 2.2 ist der Schaltungsaufbau der beiden Speicherzellen gezeigt. Zu erkennen ist hierbei der Unterschied in der Komplexität. Die DRAM-Zelle auf der linken Seite besteht aus nur einem Transistor und einem Kondensator. Die SRAM-Zelle auf der rechten Seite benötigt sechs Transistoren und zwei Inverter. Aufgrund der komplexeren Struktur ergibt sich für den SRAM der Vorteil, einfach steuerbar zu sein und er ist vergleichsweise schneller, da er keinen extra Datenbus benötigt, wie es bei DRAM der Fall ist. Auf der anderen Seite ist DRAM deutlich günstiger, was auf die niedrige Anzahl an Bauteilen und die höhere Energieeffiziez zurückzuführen ist. Aufgrund des einfachen Aufbaus ist es beim DRAM möglich eine viel höhere Speicherdichte verglichen mit SRAM zu erzielen. Deshalb dominiert DRAM auch den Markt der flüchtigen Speicher. Jedoch befindet sich fast in jedem Logik- oder Speicherchip SRAM in Form des erwähnten Pufferspeichers oder in eingebetteten Systemen, in denen nur bis zu zehntausenden an Kilobytes benötigt werden. DRAM-Speicher werden immer dort eingesetzt, wo große Datenmengen verarbeitet werden. Ein Beispiel wäre der Arbeitsspeicher für Desktops, da hier eine sehr große Speichermenge erforderlich ist [MSCT14].

Abbildung 2.2.: Schaltungsaufbau von DRAM und SRAM [MSCT14]

#### 2.1.2. Nichtflüchtige Speicher

Nichtflüchtige Speicher behalten ihre Information auch wenn sie von der Spannungsversorgung getrennt werden [MSCT14]. Daraus resultieren zwei verschiedene Anwendungsfälle. Speicher mit einer hohen Speicherdichte, d.h möglichst viel Speicherplatz auf geringer Platinenfläche und mit großem Schreibdurchsatz werden als Daten- oder Massenspeichermedium verwendet, wie beispielsweise eine SSD-Festplatte oder ein Flash-Speicherstick. Das zweite Anwendungsgebiet finden Speicher, die einen schnellen wahlfreien Zugriff benötigen und Code auf dem Speicher ausführen können. Das bedeutet, dass ein schneller Zugriff auf Speicherareale an verschiedenen Speicheradressen gegeben ist. Der schnelle Zugriff auf kleine Speicherbereiche wird durch eine stark granulare Adressierung erreicht. Diese Speicher können beispielsweise das Betriebssystem eines Mikrocontrollers speichern, wobei das Betriebsystem direkt auf dem Speicher ausgeführt werden kann [BCMV03]. Ein Beispiel hierfür wäre ein NOR-Flash-Speicher, der später noch näher erklärt wird.

Wie auf Abbildung 2.1 zu sehen ist, lassen sich auch nichtflüchtige Speicher weiter unterteilen. Die wichtigsten Unterscheidungskriterien sind hier auf der einen Seite wie ein Speicher programmiert wird und auf der anderen Seite wie und ob er gelöscht werden kann. Es gibt hersteller- und anwenderprogrammierte Speicher, die wiederum entweder nicht löschbar, durch ultraviolettes Licht löschbar oder elektrisch löschbar sind. Ein wichtiger Vertreter der herstellerprogrammierten Speicher ist der Read Only Memory (ROM), der nicht löschbar ist. Dieser eignete sich in der Vergangenheit beispielsweise, um das BIOS eines Computers zu speichern, da es nicht verändert werden darf und nur Lesezugriff bieten soll. Zum heutigen Zeitpunkt wurde jedoch der ROM durch Flash-Speicher ersetzt, da das BIOS sich nun auch gelegentlichen Updates unterziehen muss. Für nichtflüchtige Speicher ergeben sich wichtige allgemeine Anforderungen, die zur Beurteilung eines Speichers dienen [BCMV03][ARI16]:

• Niedrige Bit-Kosten

#### 2. Grundlagen Flash

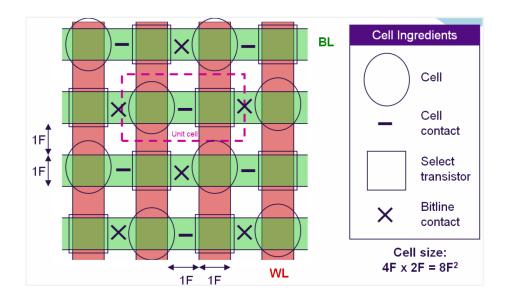

Abbildung 2.3.: Array-Layout mit einer  $8F^2$  Strukturgröße

- Hohe Flexibilität

- Programmierung mit möglichst hoher Geschwindigkeit

- Hohe Zuverlässigkeit

Die Anforderung nach niedrigen Kosten ist die wichtigste. Der Preis wird hauptsächlich durch die Die-Size (Größe eines einzelnen, ungehäußten Halbleiterchips) des Speichers und die Kosten des Herstellungsprozesses bestimmt. Daher ist es notwendig eine möglichst kleine Die-Size mit einem möglichst kostengünstigen Fertigungsprozess zu kombinieren. Um die Größe des einzelnen Chips zu reduzieren, muss die Größe der einzelnen Speicherzelle verringert werden, da die Speicherzellen einen Großteil der benötigten Fläche ausmachen. Der Begriff der sogannten "Feature-Size" ist für dieses Thema wichtig und wird auch im Verlauf dieser Arbeit öfter erwähnt, wenn es um das Thema Skalierung einer Speicherzelle geht. Sie ist eine essentielle Größe in der Halbleitertechnik und schafft Vergleichbarkeit der verschiedenen Technologien. Die Feature-Size ist die kleinste Strukturbreite, die zuverlässig fotolithographisch hergestellt werden kann. Dabei entspricht diese kleinste Strukturbreite einem "F". "Features" sind dabei beispielsweise die Flash-Einzelzelle, ein Zellkontakt, ein Auswahltransistor oder ein Bitline-Kontakt und nehmen jeweils die Strukturbreite eines Fs in Anspruch vgl. Abbildung 2.3. Das Ziel ist es eine  $4F^2$  Struktur (F steht für Feature), bei der die planare Ausrichtung (nur in der Ebene) von Auswahltransistor und Zelle den jeweils geringsten Platzbedarf aufweist und damit die maximal mögliche Dichte erreicht wird. In den Anfängen der Flash-Technologie war dies jedoch noch nicht möglich. Auf Abbildung 2.3 ist ein solches Array-Layout mit einer  $8F^2$  Strukturgröße abgebildet. Die Fläche wird hier durch die Ausdehnung und Anordnung der Einzelkomponenten innerhalb einer Einzelzelle bestimmt. Die Anforderungen für die Isolierung sind bei NAND-Flash höher als bei anderen Speichern, da diese mit einer vergleichsweise hohen Spannung konfrontiert werden. Da es durch die hohe Spannung zu Schäden an der Isolierung kommen könnte, gestaltete sich das Verringern des Durchmesser der Isolierungschicht äußerst schwierig [ARI16].

Mit Flexibilität ist die Fähigkeit gemeint, wiederholt gelöscht sowie wieder neu programmiert zu werden und dies mit einer minimalen Granularität. Dies bedeutet der Speicher muss auch in der Lage sein, kleine Speicherbereiche löschen und programmieren zu können. Die Anforderung an eine möglichst schnelle Programmierung, die in einer maximalen Schreibgeschwindigkeit des Speichers resultiert ist selbsterklärend [BCMV03].

Die Zuverlässigkeit ist auch eine essenzielle Anforderung an einen nichtflüchtigen Speicher. Dies bedeutet, dass der Speicher die Information lange genug und mit der verlangten Datenintegrität aufbewahrt. Genauere Informationen zum Thema Zuverlässigkeit folgen im Unterkapitel 2.3, nachdem der Aufbau der Flash-Zelle erläutert wurde.

Die Flash-Technologie bot dabei den besten Kompromiss zwischen den genannten Anforderungen, aufgrund einer Ein-Transistor-Zelle die öfter als 100000 mal elektrisch beschrieben werden konnte. Dabei konnte man in der Einheit Byte den Speicher beschreiben und in Pages (KiloBytes) löschen [BCMV03]. Folglich wurde die Flash-Technologie sehr stark in den folgenden Forschungsfeldern weiterentwickelt [MSCT14]:

- Verkleinerung der Zellgröße

- Verringerung des Stromverbrauchs

- Vergrößerung der Speicherdichte (Mehr Bits auf der selben Fläche)

### 2.2. Flash-Technologie

#### 2.2.1. Aufbau einer Flash-Zelle

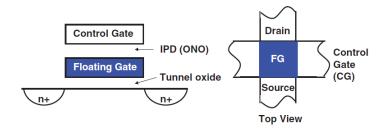

Aus Punkt 2.1.2 geht hervor, dass die Flash-Technologie eine enorm wichtige Technologie ist und ein sich stetig weiterentwickelndes Forschungsfeld. Deshalb wird sie als Exempel für nichtflüchtige Speicher in dieser Arbeit weiter betrachtet. Um die Vor- und Nachteile dieser Technologie zu verstehen, werden im Folgenden die technischen Grundprinzipien erläutert. Auf Abbildung 2.4 ist die Architektur einer einzelnen Flash-Zelle abgebildet und auf Abbildung 2.5 das daraus resultierende Schaltbild. Im Prinzip ist eine solche Zelle ein Metal Oxide Semiconductor Transistor (MOS), also ein Halbleiter-Bauelement zum Steuern elektrischer Spannungen. Ein derartiger Transistor ist identisch zur gezeigten Flash-Zelle auf Abbildung 2.4. Bei der Flash-Zelle jedoch wird ein zusätzliches Gate, das Floating Gate (FG), in das Zentrum des Transistors eingefügt. Dieses ist elektrisch komplett mit Dielektrikum isoliert und "schwebt (floating)" deswegen isoliert im Zentrum des Transistors. Aus diesem Grund ist es in der Lage Ladung zu speichern, ohne diese wieder zu verlieren. Das bedeutet aus einem reinen Steuerungselement wurde durch das Hinzufügen eines isolierten FGs eine Speicherzelle. Angesteuert (ausgewählt) wird die Speicherzelle über das Control Gate (CG) [BCMV03].

Zur Injektion und Emission von Ladung in das FG muss das sogenannte Tunneloxid, das das FG vom Rest des Transistors isoliert, überwunden und Ladung durch diese Isolationsschicht transportiert werden. Dafür gibt es generell zwei bekannte physikalische Verfahren [ARI16]:

- Fowler-Nordheim (FN)-Tunneln für Injektion und Emission

- Channel-Hot-Electron (CHE) Injection

Abbildung 2.4.: Architekur einer Flash-Einzelzelle mit Floating Gate [ARI16]

Abbildung 2.5.: Schaltbild einer Flash-Speicherzelle [MSCT14]

Wie sich diese Effekte genau erklären, soll kein Bestandteil dieser Arbeit sein. Grundsätzlich wird beim Fowler-Nordheim-Tunneln wird die Durchbruchsspannung der Isolierungsschicht herbeigeführt. Bei dieser Spannung wird also der Isolator leitend und es können Elektronen in das FG fließen. Der Effekt kann mit der Entstehung eines Blitzes verglichen werden, bei der Wolken bei einer gewissen Durchbruchsspannung in einem Blitz entladen werden. Bei der CHE ist nicht die Energie der Spannung ausschlaggebend. Die Elektronen, die ins FG injiziert werden sollen, werden so stark beschleunigt, dass die kinetische Energie der Ladung (Bewegungsenergie) ausreicht, die Isolationsschicht zu überwinden. Bei beiden Effekten kommt es zu Kollisionen von Elektronen mit dem Kristallgitter des Tunneloxids. Diese Tatsache führt zu einer allmählichen Abnutzung des Speichers. Ein wichtiger Faktor ist deshalb die Dicke des Tunneloxids. Dieses muss auf der einen Seite dünn genug sein, um die erwähnten Effekte möglich zu machen, auf der anderen Seite aber auch dick genug sein, um sich nicht zu schnell abzunutzen. Genaueres zur Zuverlässigkeit und somit auch den Abnutzungserscheinungen der Flash-Zelle wird in Unterkapitel 2.3 erläutert.

Zusammenfassend lässt sich feststellen, dass der grundlegende Aufbau der Flash-Zelle mit seiner Hochspannungsprogrammierung zu einer allmählichen Abnutzung führt, im Gegensatz zu anderen Speichern. Auf diese Abnutzung muss, wie später noch erklärt wird, reagiert werden. Der Speicher muss also auf gewisse Weise schonend betrieben werden, was wiederum einen essentiellen Einfluss auf die Performance bedeutet.

#### 2.2.2. Architekturen

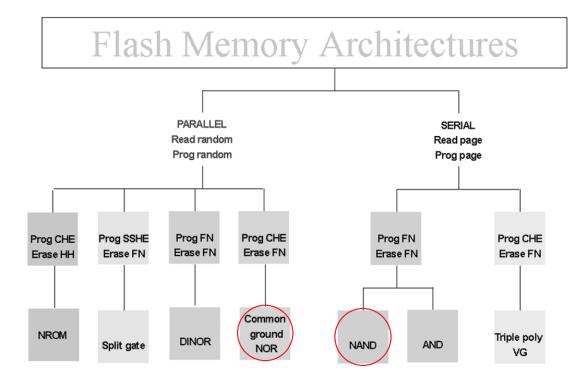

Nachdem die Grundlagen der einzelnen Flash-Zelle dargelegt wurden, ist es interessant sich die aus den Einzelzellen zusammengeschlossenen Speicher-Arrays anzusehen. Dabei werden zwei Zugriffstypen unterschieden. Es kann entweder parallel oder seriell auf das Speicherarray zugegriffen werden. Auf Abbildung 2.6 können diese beiden Hauptkategorien erkannt werden.

Abbildung 2.6.: Flash Architekturen [BCMV03]

Die zwei Vertreter sind der NOR-Flash-Speicher beim parallelen Zugriff und der NAND-Flash-Speicher beim seriellen Zugriff [BCMV03].

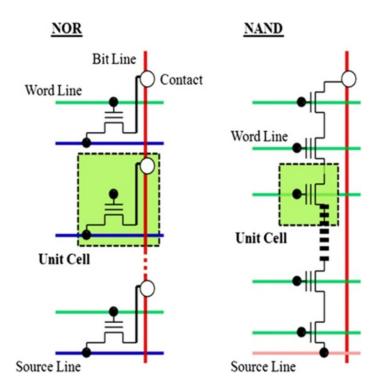

Die Namensgebung bezieht sich wiederum auf die Zugriffsstrukturen der beiden Speicher und kommt aus der Complementary Metal Oxide Semiconductor (CMOS)-Technik. Die CMOS-Technik ist die Logikfamilie, die hauptsächlich für integrierte Schaltkreise verwendet wird, d.h die Struktur für die elementaren Logikgatter (z.B. AND-Gatter) stellt. Auf Abbildung 2.7 sind die beiden Architekturen von NOR und NAND Speicherarrays zu sehen. Die parallele Verbindung des NOR-Arrays erinnert an die Verbindung der Transistoren in einem logischen NOR-Gate aus der CMOS-Technik. Die serielle Verbindung des NAND-Arrays erinnert wiederum an ein logisches NAND-Gate. Intel ist das Unternehmen, das 1988 den ersten NOR-Speicherchip auf den Markt gebracht hatte. Toshiba war der Vorreiter in Sachen NAND und brachte den ersten auf dieser Technologie basierten Speicherchip 1989 auf den Markt [MSCT14].

Die Vor- und Nachteile der beiden Technologien können auch von ihren jeweiligen Zugriffstypen abgeleitet werden. Da die Zellen des NOR parallel mit der Bitline (siehe Abbildung 2.7) verbunden sind, können diese Zellen individuell gelesen und programmiert werden. NOR bietet Adress- und Datenbusse, um wahlfrei auf Speicherbereiche zuzugreifen. Es handelt sich also um eine Random-Access-Schnittstelle. Dies ermöglicht neben einem schnellen Lesen und Schreiben von einzelnen Bytes auch einen Execute in Place (XiP), d.h ein Ausführen des Codes direkt auf dem Speicher, anstatt den Code in den Arbeitsspeicher zu kopieren und dann auszuführen. Grund dafür ist die besagte Random-Access-Schnittstelle mit ihrer feinen Adressierung, bei der schnell auf kleine Speichereinheiten zugegriffen werden und Beim NAND hingegen kann nur auf vergleichsweise große Bereiche zugegriffen werden und

Abbildung 2.7.: Vergleich von NOR- und NAND-Speicherarrays [MSCT14]

deswegen wäre ein NAND zu langsam in der wahlfreien Lesegeschwindigkeit für diesen Anwendungsfall. Der XiP ist bei eingebetteten Applikationen beispielsweise erforderlich. Es ergeben sich aus dieser Architektur allerdings auch Nachteile. So ist die Performance bei Schreib- und Löschoperationen bei größeren Dateien (nicht individuelle Bytes) im Vergleich eher langsam. Dies kann durch den erzeugten Overhead begründet werden, der durch die Addresierung von vielen kleinen Einheiten für die Programmierung (Löschung) entseht. Außerdem verbraucht der parallele Ansatz deutlich mehr Fläche und erzeugt somit geringere Speicherdichten. Aus diesem Grund sind die wirtschaflich produzierten NOR-Speicher immer vergleichsweise klein (Speicherkapazität). Typischerweise haben NOR-Speicher eine Größe von mehreren KB bis hin zu einigen Gbit. Folglich werden NOR-Speicher als Codespeicher gerade für eingebettete Systeme verwendet, sind aber auch perfekt als Ersatz für ROM-Speicher geeignet, um das BIOS/Firmware zu speichern. Auch in Low-End-Mobiltelefonen oder Konsumgeräten werden diese verbaut [MSCT14].

Aufgrund der seriellen Verbindungsstruktur des NAND-Speichers, ergeben sich mehrere Vorteile gegenüber dem NOR. Die serielle Verbindung benötigt weniger Fläche, was eine höhere Speicherdichte zur Folge hat. Diese wiederum bewirkt, dass die Kosten pro Bit niedriger sind und außerdem aufgrund des niedrigeren Platzverbrauchs höhere Speichergrößen möglich sind. Ein klarer Vorteil liegt auch in der höheren Geschwindigkeit bei Schreib- und Leseoperationen größerer Datenmengen, da bei der seriellen Schnittstelle mehrere Zellen gleichzeitig angesprochen werden. Es ergeben sich auch Nachteile aus dem seriellen Ansatz. Performancenachteile entsehen beim NAND-Speicher bei zufälligem Zugriff auf Speicherbereiche, da dieser keine Random-Access-Schnittstelle sondern eine sequentielle Schnittstelle besitzt. Dies kann nur auf Systemebene erzielt werden, nicht jedoch auf Hardware-Ebene.

Abbildung 2.8.: Array-Architektur von NAND-Speicherzellen [ARI16]

Dazu kann der Vergleich zu einem Betriebsystem herangezogen werden, bei dem es scheinbar möglich ist gleichzeitig mehrere Prozesse auszuführen. Es findet jedoch keine echte Gleichzeitigkeit statt, sondern eine geschickte zeitliche Planung, die den Eindruck der Gleichzeitigkeit erweckt. Aus diesen Eigenschaften ergibt sich, dass NAND-Speicher hervorragend als größere Datenspeicher für beispielsweise Memory Cards geeignet sind um große Dateien, wie Videooder Audiodateien zu speichern [MSCT14].

Unter Betrachtung der vorhergehenden Vor- und Nachteilen kann geschlussfolgert werden, dass der NAND-Speicher ideal als Datenspeicher für den Automotive-Bereich geeignet ist, wenn Speichergröße und Lese- und Schreibgeschwindigkeit betrachtet werden. Somit werden die Analysen und Tests in dieser Arbeit anhand von NAND-Speichern durchgeführt. Auf Abbildung 2.8 ist die spezielle NAND-Array-Architektur noch etwas genauer dargestellt. Um später in Unterkapitel 2.2.3 den Lese- und Schreibvorgang zu verstehen, müssen die Grundzüge der Array-Architektur bekannt sein.

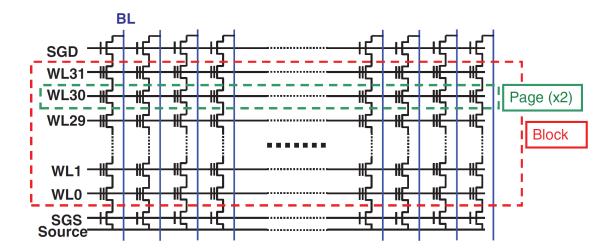

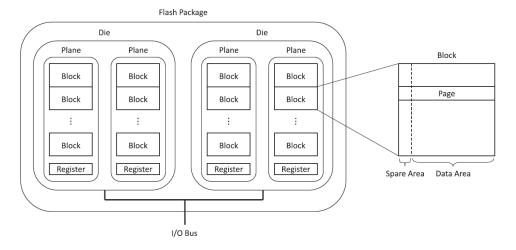

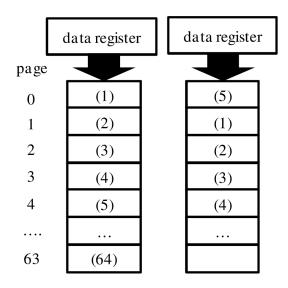

Die blauen vertikalen Verbindungen stellen die Bitlines(BL) dar. Eine BL verbindet alle Transistoren innerhalb eines NAND-Zellen-Strings. Dieser String besteht hier aus 32 Zellen sowie zwei Auswahltransistoren. Die 32 Zellen sind in Serie verbunden und die zwei Auswahltransistoren (SGD, SGS) existieren, um diese Serie gegenüber Source und Drain isolieren zu können, soweit dies benötigt wird. Die horizontalen Leitungen nennen sich Wordlines (WL) und verbinden immer die Zellen mit der selben Nummer von verschiedenen Bitlines (z.B. WL0 schließt alle Zellen mit der Nummer null in horizontaler Richtung zusammen). Die Zellen einer WL bilden eine sogenannte Page (auf der Abbildung in grün). Diese ist typischerweise 2KB bis 16 KB groß. Ein Block (auf der Abbildung rot) wiederum hat die Größe: Page \* 32 Zellen \* 2 = 128 KB bis zu 1024 KB. Der Faktor zwei kommt hinzu, da 64 Pages in einem Block sind. Gelesen und geschrieben wird auf Page-Ebene und gelöscht auf Block-Ebene.

Zusammenfassend lässt sich hinsichtlich der Architektur festhalten, dass NAND-Flash mit seinem seriellen Zugriff auf die Einzelspeicherzellen die Flash-Variante für große Speicherdichten repräsentiert. Die Array-Architektur zeigt, wie die physikalischen Zellen auf logische Einheiten (Pages, Blöcke) abgebildet und gesteuert (BL, WL) werden. Mit diesen Informationen können nun der Lese-, Schreib- und Löschvorgang im Hinblick auf die physische

Abbildung 2.9.: Prinzip des Lesevorgangs einer Flash-Einzelzelle [ARI16]

und logische Auswirkung verstanden werden und somit auch die sich daraus ergebenden grundlegenden Performancecharakteristka dieser Operationen.

#### 2.2.3. Lese- und Schreibvorgang

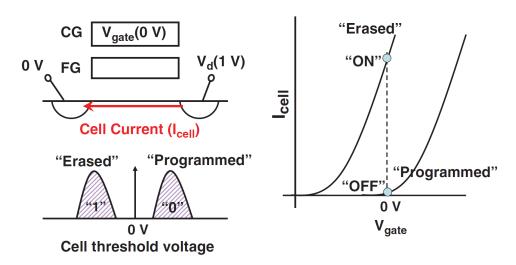

Da bereits die Architektur der Einzelzelle und des NAND-Zellen-Arrays bekannt sind, wird nun erklärt, wie diese Technologie das Lesen und Schreiben ermöglicht. Der Effekt, der das Lesen von Information ermöglicht, ist das schon erwähnte Speichern und Entladen des FG. Dies verdeutlicht Abbildung 2.9. Das grundlegende Funktionsweise der Flash-Zelle ist wie folgt: Wenn Ladung im FG gespeichert wird, so ändern sich die elektrischen Eigenschaften des gesamten Bauteils, da die aufgebrachte Ladung zusätzlich isolierend wirkt. Dies hat den Effekt, dass die Flash-Zelle am CG mit einer höheren Spannung aktiviert werden muss, damit die Zelle wieder Strom (Ic) leiten kann. Man nennt diese Spannung Zellgrenzspannung und die Verschiebung eine Grenzverschiebung. Jene Eigenschaft macht man sich nun zu nutze und setzt das CG auf eine gewisse Kontrollspannung (Vgate = 0V), wie in der Abbildung auf der rechten Seite zu sehen. Prüfsensoren kontrollieren dabei, ob ein Stromfluss entsteht. Ergibt sich kein Stromfluss, so kann schlussgefolgert werden, dass die Zelle programmiert ist, d.h. es befindet sich zusätzlich isolierende Ladung im FG. Kein Stromfluss wird also als eine logische 0 oder "OFF"erkannt. Fließt unter der angelegten Kontrollspannung ein Strom durch den Transistor, so kann geschlussfolgert werden, dass die Zelle gelöscht ist und damit einer logischen 1 oder dem Zustand "ON"entspricht [ARI16].

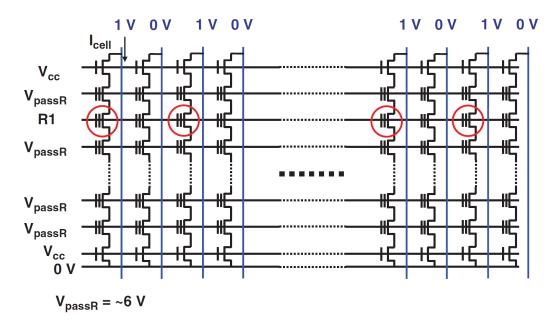

Aus Abbildung 2.10 lässt sich schließen, wie die einzelnen Elemente gesteuert werden, sodass gewisse Zellen ausgelesen werden können. Gelesen wird immer eine Page, also eine Reihe von Zellen, die durch eine einzige WL angesprochen wird. Die WL steuert dabei alle CGs in dieser Line. An der zu lesenden WL werden die genannten Vgate = 0V zur Lesekontrolle angebracht. Alle anderen nicht ausgewählten WLs werden auf VpassR = 6V gesetzt. Bei einer derart hohen Spannung werden alle Transistoren leitend und agieren somit als sogenannte Durchlasstransistoren. Die Informationen werden folglich weitergeleitet. An den zu lesenden Einzelzellen wird die jeweilige BL, die immer die Source des Transistors steuert auf 1V gesetzt, um eine Spannung zwischen den 0V Drain und der Source zu erzeugen.

Abbildung 2.10.: Schaltung einer Leseoperation bei einem NAND-Array [ARI16]

Die BLs der nicht auszulesenden Einzelzellen werden somit auf 0V geschaltet. Es lässt sich folgende Erkenntnis schließen: die nicht ausgewählten Zellen, beziehungsweise die Zellen, deren WL auf 6V (hohe Spannung) geschaltet wurden, bekommen eine hohe Spannung ab um leitend zu werden. Dieser Umstand kann dazu führen, dass diese Transistoren gestört werden. Eine detaillierte Erklärung gibt Unterkapitel 2.3 [ARI16].

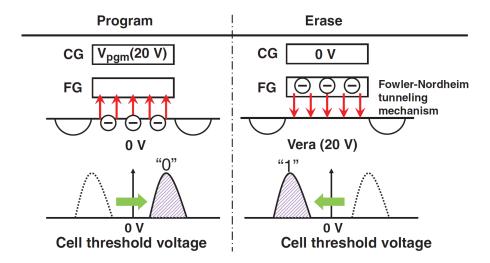

Eine Einzelzelle wird programmiert und eine Grenzspannungsverschiebung erzeugt. Durch eine hohe Spannung am CG und gleichzeitig niedrige Spannung am Substrat wird Ladung durch das Tunneloxid ins FG injiziert (programmiert). Um den Speicher zu löschen, wird genau das Gegenteil gemacht. Dies ist auf Abbildung 2.11 anschaulich verdeutlicht.

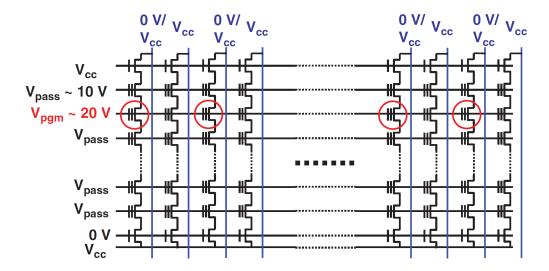

Auf Abbildung 2.12 ist die Programmierung eines NAND-Flasharrays zu sehen. Es wird immer eine WL tiefer von oben angefangen programmiert. Die WL der nicht zu programmierenden Zellen werden, ähnlich wie bei der Leseoperation, mit einer hohen Spannung durchlässig geschaltet. Die BL der zu programmierenden Zelle wird dann auf 0V gesetzt, um ein maximales Spannungsgefälle zwischen FG und Substrat zu erzeugen. So kann Ladung in das FG injiziert werden. Beim Löschvorgang wird das Spannungsgefälle einfach umgedreht. Die Löschoperation wird jedoch nicht mit einzelnen WLs ausgeführt, sondern gleichzeitig auf einem gesamten Block. Sowohl Programmier- als auch Löschoperation sind andauernde Vorgänge und keine einmaligen Operationen. Das bedeutet, nachdem Elektronen bewegt wurden, muss immer kontrolliert werden, ob die Aktion erfolgreich war. Deshalb wird in Pulsen programmiert und gelöscht. Es wird also ein Spannungspotential für eine kurze Dauer (z.B.  $200\mu$ s) angelegt und von einer kurzen Kontrollspannung (Verify) gefolgt, die den Erfolg der Aktion kontrolliert. Dauer und Potenial des Spannungspulses sind hier die essentiellen Faktoren, die Löschen vom Schreiben unterscheiden. Je "mächtiger"der Puls (Spannung, Dauer), desto schneller bewegen sich genug Elektronen, um den erwünschten Zustand zu erzielen. Damit wird jedoch die Aktion gleichzeitig destruktiver für den Speicher. Es muss also ein Gleichgewicht zwischen Performance und Zuverlässigkeit gefunden wer-

Abbildung 2.11.: Löschen und Programmieren einer Flash-Einzelzelle [ARI16]

den. Programmiert kann dementsprechend deutlich schneller als gelöscht werden, da beim Löschen alle Zellen in einem Speicherarray gleichzeitig unter hoher Spannung stehen und deswegen besonders stark abgenutzt werden. Deshalb werden die Pulse hier kürzer und über einen längeren Zeitraum ausgeführt. Folglich ergibt sic die Tatsache, dass eine Schreibaktion im  $\mu$ s-Bereich und eine Löschaktion im ms Bereich liegt, also deutlich langsamer ist[ARI16].

Zusammenfassend kann hier festgehalten werden, dass sich aus dem physikalischen Vorgang des Elektronentransports in den Flash-Zellen unterschiedliche Performance- und Haltbarkeitseigenschaften ableiten lassen. Leseaktionen sind im Vergleich am schnellsten (ca.  $15\mu s$ ) und am wenigsten destruktiv für die Speicherzelle, aufgrund niedriger Kontrollspannung. Schreib- und Löschaktionen sind deutlich langsamer (Schreiben  $200\mu s$ , Löschen 2ms), wobei die Löschaktion die Zelle am deutlichsten strapaziert. Löschoperationen müssen folglich so gut es geht vermieden werden. Dies ist Aufgabe des Controllers und wird in Unterkapitel2.5.2 behandelt.

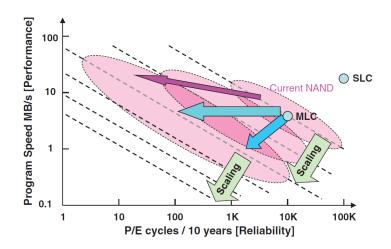

#### 2.2.4. Multilevel-Zellen

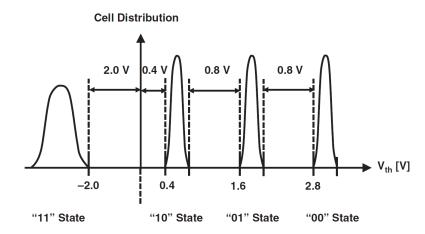

Die Idee bei diesem Ansatz ist es, die Speicherdichte zu vergrößern, ohne dabei die physikalische Größe der Zelle zu verändern. Möglich ist das, in dem ein FG die Fähigkeit besitzt, verschiedene Mengen an Ladung aufzunehmen. Folglich bewirken dann auch verschiedene Grenzspannungen den Stromfluss der Flash-Zelle. Abbildung 2.13 zeigt den Multilevelansatz mit seinen vier verschiedenen Grenzspannungen. Diese Spannungen korrespondieren jeweils mit einer bestimmten Bitfolge. Bei dem ersten Multilevel-Ansatz, der sogenannten Multi Level Cell (MLC), werden hierbei zwei Bit an Information darstellbar. Außerdem gibt es noch die Triple Level Cell (TLC), bei der 3 Bits zu Verfügung stehen und die Quad Level Cell (QLC), bei der sogar 4 Bit an Information innerhalb einer einzigen Flashzelle gespeichert werden können. Die Art von Einzelzelle, die vorher besprochen wurde und nur ein einzelnes Bit speichern kann, wird Single Level Cell (SLC) genannt. Die Struktur der Einzelzelle und der Herstellungsprozess sind im Prinzip bei SLC und MLC gleich. Neben dem offensichtlichen Vorteil der erhöhten Speicherdichte pro Zelle bringt dieser Ansatz jedoch auch Hürden mit sich. Damit mehrere Zustände gelesen werden können, müssen die Span-

Abbildung 2.12.: Programmierung eines NAND-Flasharrays [ARI16]

nungskurven enger werden und näher zusammenrücken, wie auf Abbildung 2.13 zu erkennen ist. Auf dieser Darstellung wird allerdings "nur"eine MLC mit 2 Bit Information gezeigt. Dies lässt erahnen, wie genau diese Verteilung bei einer QLC werden muss. Natürlich kann es bei einer solchen Zelle mit schmäleren Kurven und somit einem kleineren Bereich, der vom Sensor als die richtige Information ausgelesen wird, schneller dazu kommen, dass eine falsche Information ausgelesen wird. Gerade im Hinblick auf Abnutzung, sind diese Zellen deshalb deutlich schlechter, da die Zustände schneller nicht mehr erkannt werden können. Außerdem müssen diese Zellen bei der Schreiboperation viel genauer programmiert werden. Somit steigt die Schreibdauer pro Bit und damit sinkt die Schreibgeschwindigkeit. Um diesen negativen Effekten entgegenzuwirken, wurde auf Systemebene der "Moving Read Algorithmus" entwickelt. Dieser passt intelligent die Auslesespannung am ausgewählten CG den von physikalischen Effekten beeinflussten Grenzspannungen an. Dies erhöt deshalb die Haltbarkeit. Aus den negativen Eigenschaften kann geschlussfolgert werden, dass Multilevel-Zellen zwar größere Speichermengen ermöglichen, jedoch in der Qualität Defizite mit sich bringen. Dabei gilt, je mehr Bit pro Zelle gespeichert werden sollen, desto schlechter wird die Qualität. Deshalb werden TLC-Speicher beispielsweise für USB-Speichersticks verwendet, da hier ausschlaggebend ist möglichst viel Daten auf kleinstem Raum abzusichern, jedoch ein geringer Datenverlust tolerierbar ist [ARI16].

Die aufgeführten Punkte bringen die Erkenntnis, dass mit einer steigenden Anzahl an Bits pro Zelle die Speicherdichte des Flash-Speichers steigt, jedoch die Zuverlässigkeit und die Performance sinken. Die Performanceeinbusen werden durch einen umfangreicheren Kontrollprozess bei den Operationen (Lesen, Schreiben, Löschen) auf der Flash-Zelle bedingt, da hier mehrere Spannungszustände als ursprünglich zwei (SLC) unterschieden werden müssen und somit genauer gearbeitet werden muss. Die Zuverlässigkeit sinkt, da es schneller durch Abnutzung zu dem Situation kommt in der nicht mehr alle Zustände verlässlich unterschieden werden können, da es bereits ausreichend ist, wenn wenige Elektronen verloren gehen, um eine dauerhafte Grenzspannungsverschiebung zu bewirken.

Abbildung 2.13.: Verteilung der Grenzspannungen auf vier Zustände bei Multilevel-Zelle [ARI16]

### 2.3. Zuverlässigkeit

In diesem Unterkapitel werden die diversen Hürden der Flash-Technologie besprochen, die beispielsweise den Prozess der Erhöhung der Speicherdichte oder die Steigerung der Performance beeinträchtigen.

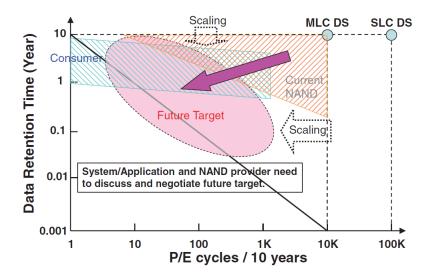

#### 2.3.1. Data Retention

Der Begriff "Data Retention" definiert sich als die Fähigkeit eines Speichers seine Information über einen längeren Zeitraum speichern zu können. Wie auch andere nichtflüchtige Speicher, sind Flash-Produkte spezifiziert ihre Information über zehn Jahre zu behalten. Das bedeutet, dass der Verlust an Ladung im FG über die Jahre hinweg minimal bleiben muss, um noch die richtigen Zustände auslesen zu können. Bei modernen Flash-Speichern ist die Zellgröße sehr stark geschrumpft und damit auch die Kapazität der Zelle. Verliert die Zelle 20 % ihrer Ladung (einige Elektronen pro Monat), kann dies schon zum Auslesen eines falschen Wertes führen. Die größten Probleme bei der Data Retention haben Zellen, die ihren programmierten Zustand beibehalten müssen, da der programmierte Zustand mit einem elektronenbefüllten FG korrespondiert [BCMV03].

Es gibt mehrere Gründe für den Verlust der Ladung [BCMV03]:

- Defekte im Tunneloxid

- Defekte in der Isolationsschicht (Dielektrikum)

- Kontamination durch mobile Ionen

- Das Freilassen von Ladung aus der Isolationsschicht rund um das FG

Die Data Retention ist abhängig von mehreren Charakteristiken. Es gibt sogenannte "Program and Erase (P/E) Schemes". Diese Schemata beinhalten im Prinzip die Information, mit welchen Verfahren Programmier- und Löschoperationen durchgeführt werden. Beispielsweise kann solch ein Schema festlegen, dass anhand des Fowler-Nordheim-Effekts programmiert wird und ein anderer Effekt für das Löschen verwendet wird. Welches Schema

Abbildung 2.14.: Schätzung der Data Retention-Zeit im Bezug auf die Betriebstemperatur [ARI16]

nun verwendet wird hat enormen Einfluss auf die Dauer der Data Retention. Aus der Forschung ging hervor, dass ein spezielles Schema, das "Uniform Program and Erase Schema"die Data Retention enorm steigern kann [ARI16].

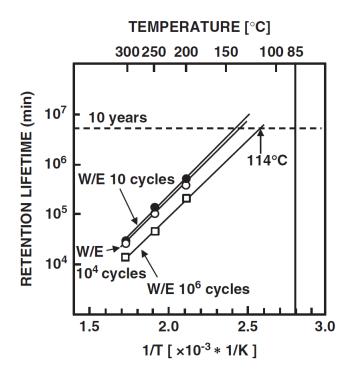

Ein weiterer Faktor ist der Gebrauchszustand des Speichers im Hinblick auf P/E-Cycles. In Unterkapitel 2.2.3 wurde der Lese- und Schreibvorgang bereits erläutert. Es wird in der Einheit Block (bestehend aus mehreren Pages) gelöscht und in der kleineren Einheit Page geschrieben. Ein P/E-Cycle ist nun der Vorgang des einmaligen Löschens eines Blockes mit anschließender Beschreibung aller Pages innerhalb dieses Blockes, bis dieser sozusagen voll ist und wieder gelöscht werden müsste. Es zeigt sich, dass P/E-Cycling die Data Retention-Zeit verkürzt. Jedoch wirkt das Uniform P/E Schema diesem Effekt in einem gewissen Maße entgegen und lässt auch noch bei einer P/E-Cycle-Anzahl von einer Millionen eine akzeptable Data Retention von zehn Jahren zu. Der negative Effekt bleibt jedoch erhalten [ARI16].

Der nächste Faktor ist Temperaturabhängigkeit. Eine erhöhte Temperatur (150-300 Grad Celsius) führt zu einer deutlich verkürzten Data Retention-Zeit. Je höher dabei die Temperatur ist, desto stärker ist dabei dieser Effekt zu beobachten. Dies wird durch das vorher besprochene P/E-Cycling noch verstärkt. Mit dem Wissen über die Temperaturabhängigkeit kann die Data Retention über Zeit durch eine erhöhte Temperatur simuliert werden. Auf Abbildung 2.14 wurde dieser Ansatz verwendet und eine Schätzung der Data Retention Zeit im Bezug auf die Betriebstemperatur und die vorher getätigten P/E-Cycles dargestellt. Hier zeigt sich, dass bei einer Betriebstemperatur von 100°C die besagten zehn Jahre Data Retention-Zeit auch bei 1 Millionen P/E-Cycles garantiert werden können [ARI16].

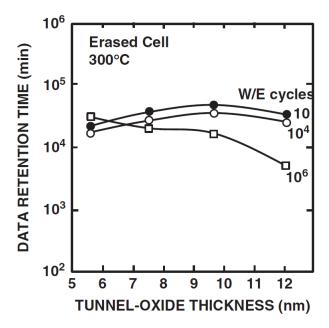

Ein weitere wichtige Einflussgröße bildet die Dicke des Tunneloxids. Auf Abbildung 2.15 ist ersichtlich, dass diese Beziehung nicht linear und nicht intuitiv ist. Für die dünnen Tunne-

Abbildung 2.15.: Data Retention-Zeit bei 300°C in Abhängigkeit der Tunneloxiddicke und den P/E-Cycles[ARI16]

loxidschichten verkürzt sich die Data Retention-Zeit bei 10-10.000 P/E-Cycles, also im niedrigen bis mittleren Abnutzungsbereich. Jedoch bei 1 Millionen P/E-Cycles, also einer enormen Abnutzung verlängert sich diese wieder erkennbar. Dafür verantwortlich sind spezielle physikalische Effekte, deren Erläuterung den Rahmen dieser Arbeit überschreiten würden. Als Schlussfolgerung lässt sich demnach feststellen, dass die Data Retention-Zeit im Extremfall der starken Abnutzung (1 Million P/E-Cycles) nicht durch die Dicke der Tunneloxidschicht limitiert wird. Jedoch wirkt sich eine sehr dünne Oxidschicht sehr wohl im nutzerrelevanten Abnutzungsbereich negativ auf die Data-Retention-Zeit aus.

#### 2.3.2. Read/Program Disturb

Bei Read/Program Disturbs handelt es sich um einen Fehlermechanismus, bei dem eine Zelle beim Schreib- oder Lesevorgang ungewollt in ihrer elektrischen Eigenschaft (Grenzspannung) verändert wird. Die Veränderung wird durch elektrische Beanspruchung bedingt, die auf eine Zelle wirkt, während andere Zellen programmiert oder gelesen werden. Der Grund hierfür ist die Architektur der Flash-Zelle und wurde bereits in Kapitel 2.2.3 beschrieben. Da alle nicht beteiligten Zellen beim Lese- oder Schreibvorgang durchlässig geschaltet werden müssen und dafür eine relativ hohe Spannung notwendig ist, werden diese Zellen abgenutzt. Es gibt zwei Arten von Disturbs (Störungen):

- Row Disturbs

- Column Disturbs

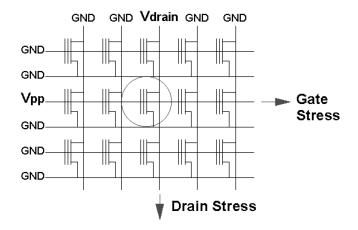

Abbildung 2.16 zeigt diese beiden Beanspruchungssarten. Row Disturbs werden durch elektrische Beanspruchung am CG bedingt. Dieser entsteht, wenn andere Zellen in der selben WL programmiert oder gelesen werden. Wenn eine hohe Spannung am CG angelegt

Abbildung 2.16.: Schema eines Flash-Arrays, das durch P/E-Cycles entstandene Row und Column Disturbs zeigt[BCMV03]

wird, müssen alle anderen Zellen in dieser Reihe dem elektrischen Stress trotzen und ihre Ladung behalten. Abhängig von den Daten, die in der Zelle aufbewahrt werden, können diese entweder durch einen Ladungsverlust am FG oder durch einen Verlust am Dielektrikum verloren werden [BCMV03].

Column Disturbs werden durch elektrischen Stress an der Drain einer Zelle beim Lese- oder Schreibvorgang einer anderen Zelle auf der selben BL bedingt. Somit können programmierte Zellen ihre Ladung vom FG an die Drain verlieren. Dies nennt sich "Soft Erasing" und erfolgt durch FN-Tunneln. Diese Störung hängt stark von der Anzahl an Zellen innerhalb einer BL und einer WL ab [BCMV03].

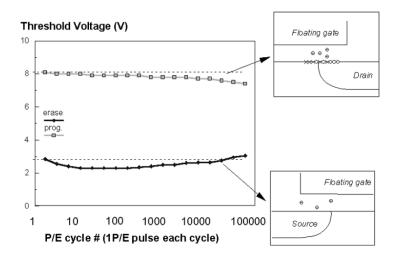

# 2.3.3. Program/Erase Standhaftigkeit

Generell sind Flash-Produkte für ca. 100.000 P/E-Cycles spezifiziert (kann für verschiedene Industriestandards abweichen). Dabei ist es bekannt dass das P/E-Cycling eine gleichmäßige Verschlechterung der Zell-Performance bewirkt. Dafür verantwortlich ist hauptsächlich die Abnutzung des Tunneloxids, welche die Standhaftigkeit der Zelle limitiert. Auf Abbildung 2.17 ist zu erkennen, wie sich über die fortschreitenden P/E-Cycles die Programmier- sowie die Löschgrenzspannung gegenseitig annähern und somit ein immer kleiner werdendes "Fenster schließen". Die Fensterbildung ist ein Maß für die Alterung des Tunneloxids und somit einer Speicherzelle. Bei Implementierungen von Flash-Produkten werden intelligente Algorithmen verwendet, um diese Fensterbildung zu verhindern. Dabei entsteht der Nebeneffekt, dass sich sowohl die Programmier- als auch die Löschzeiten der Zelle verlängern. Die Verlängerung jener Zeiten, ist ein wichtiger Hinweis auf die Performanceverminderung bei gealterten Speichern [BCMV03].

Sehr wichtig für dieses Thema ist auch die Erkenntnis, dass es mehrere Trade-Off Beziehungen im Bezug auf das P/E-Cycling gibt. Die Abbildungen 2.18 und 2.19 zeigen diese Trade-Off-Beziehungen. Die Data Retention-Zeit ist immer ein Kompromiss mit der Ausdauer bei den P/E-Cycles. Das bedeutet bei der Erstellung eines NAND-Flash-Produktes muss genau festgelegt werden, welche Prioritäten wichtig für den Kunden sind. Also entweder eine sehr lange Data Retention-Zeit oder eine sehr hohe Ausdauer oder ein Kompromiss

Abbildung 2.17.: Bilden eines Spannungsfensters als eine Funktion von P/E-Cycles bei einer Flash-Einzelzelle [BCMV03]

mit Mittelwerten aus beiden Feldern. Dieselbe Beziehung gilt auch für die Programmiergeschwindigkeit und die Ausdauer beim P/E-Cycling. Je höher die Performance bei der Schreibgeschwindkeit, umso niedriger wird die Ausdauer [ARI16].

Hinsichtlich der Zuverlässigkeit ist zusammenfassend festzustellen, dass dieses Thema besonders die Schreib- und Löschaktionen (z.B. P/E-Cycles) betrifft, auch wenn das Lesen durchaus negative Nebeneffekte (Read Disturb) erzeugen kann. Die Zuverlässigkeit hat nur einen indirekten Einfluss auf diese Arbeit, der sich jedoch massiv auswirken kann. Da die Zuverlässigkeit des Flash-Speichers in vielen Applikationen (gerade im automotiven Umfeld) hohe Priorität besitzt, muss dieses Thema von den Speicherherstellern adressiert werden. Es ist vereinfacht gesagt notwendig zusätzlichen Aufwand zu betreiben, um Daten aufzufrischen und somit die Data Retention zu verlängern. Vor allem muss effizient mit Löschaktionen umgegangen werden. Folglich entsteht zusätzlicher Mehraufwand im Speicher, den der Benutzer (Host) nicht bewusst steuert und der einen essentiellen Einfluss auf die Performance hat. Es ist also wichtig zu wissen, dass gewisse Eigenschaften, die sich positiv auf die Zuverlässigkeit des Speichers auswirken, gleichzeitig einen negativen Einfluss auf die Performance haben. Eine detailliertere Beschreibung folgt im Unterkapitel2.5.2.

# 2.4. 3-D-Architektur

Dieser Teil der Arbeit dient dazu, ein Verständnis für den technologischen Wandel in der NAND-Flash-Technologie vermittelt werden. Der treibende Faktor für diesen Wandel war das Erreichen einer höheren Speicherdichte, da dadurch der Preis pro Bit sinkt und somit Kosten gespart werden können.

#### 2.4.1. 2D zu 3D

Die bisher beschriebene Architektur der Flash-Technologie wird als 2-D-Architektur bezeichnet, da die Einzelzellen in einer planaren Struktur angeordnet sind. Diese Architektur stößt jedoch aktuell schon an ihre Skalierungsgrenzen. Um eine höhere Speicherdichte zu erlangen

Abbildung 2.18.: Trade-Off zwischen Data Retention-Zeit und P/E-Cycles[ARI16]

Abbildung 2.19.: Trade-Off zwischen Pr<br/>grammiergeschwindigkeit und P/E-Cycles [ARI16]

| Number o   | f alact | trone | nor | logic | اميرما |

|------------|---------|-------|-----|-------|--------|

| Nullibel C | il elec | เกษกร | pei | iogic | ievei  |

| Node               | 45nm | 32nm | 22nm | 16nm | 11nm | 8nm |

|--------------------|------|------|------|------|------|-----|

| SLC<br>(2 levels)  | 400  | 200  | 100  | 50   | 25   | 13  |

| MLC<br>(4 levels)  | 140  | 70   | 35   | 18   | 10   | 5   |

| TLC<br>(8 levels)  | 60   | 30   | 15   | 8    | 4    | 2   |

| QLC<br>(16 levels) | 30   | 15   | 8    | 4    | 2    | 1   |

Abbildung 2.20.: Gespeicherte Elektronenanzahl bei verschiedenen Strukturgrößen und Bittiefen pro Zelle [ARI16]

gab es nach der Entwicklung der MLC, bei der mehrere Bits in einer Zelle gespeichert werden konnten, nur noch die Möglichkeit, die Feature Size der einzelnen Zelle weiter zu verkleinern. Das Kapitel 2.3 erläuterte bereits, dass diese Schrumpfung, besonders die Reduzierung der Tunneloxidicke, zu Problemen in der Zuverlässigkeit führen kann und gewissermaßen an eine Grenze des technisch Realisierbaren kam. Abbildung 2.20 verdeutlicht die Skalierungsprobleme der 2D-Technologie. Hier wird gezeigt, wie viele Elektronen eine Flash-Einzelzelle, bei gewissen Strukturgrößen und verschiedenen Bittiefen pro Zelle speichert. Die eingezeichnete Diagonale zeigt, ab wann die Elektronenanzahl pro Zelle zu niedrig wird, um die Technologie zu realisieren. Eine SLC-Zelle mit einer 8nm-Technolgie kann beispielsweise nicht mehr realisiert werden, da die 13 Elektronen pro Zelle nicht mehr ausreichen, um die zwei verschiedenen Zustände der Zelle darzustellen und auszulesen. Dabei wird klar, dass die Strukturgröße eine klare Grenze für die 2D-Technologie darstellt. Aus diesem Grund wurde seit 2007 die Forschung an einem gänzlich innovativem Ansatz begonnen. Die 3-D-Architektur wurde vorgeschlagen. Die erste vorgeschlagene Architektur war die sogenannte Bit Cost Scalable Technology (BiCS). Diese Speicher konnten nun in der Vertikalen wachsen und somit musste die einzelne Zelle (Feature Size vgl. Unterkapitel 2.1.2) an sich nicht mehr verkleinert werden [ARI16].

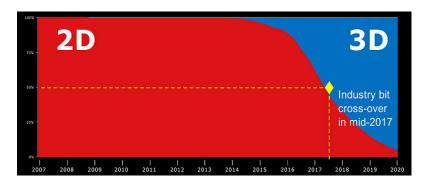

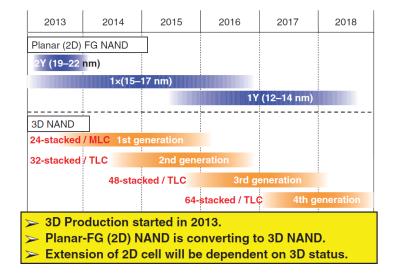

Aufgrund der deutlich vorteilhafteren Architektur wurden enorme Investitionen in der 3-D-Forschung getätigt und ab 2013 wurde schließlich der erste 3-D-Speicher in den Markt eingeführt. Dieser war ein MLC mit 24 Schichten. Die verwendete 3-D-Technologie war dabei der sogenannte *Vertical NAND (V-NAND)*. Folglich setzte sich 3D auch auf dem Markt immer stärker durch und überholte 2D im Bezug auf verkaufte Bits Mitte des Jahres 2017, wie auf Abbildung 2.21 zu erkennen ist <sup>1</sup>. Hier ist der Cross-Over-Punkt der beiden Technologien zu erkennen [ARI16].

Die Abbildung 2.22 stellt die zeitliche Entwicklung ab 2013 von 2D und 3D dar. Hier können die zwei verschiedenen Entwicklungstrends beobachtet werden. Während die 2D-Technologie auf immer kleinere Zellstrukturen setzt, wird im 3D-Bereich die Anzahl der

$<sup>^1\</sup>mathrm{Pr\ddot{a}sentation}$ von Sandisk zu 3D-NAND https://www.slideshare.net/sandisk/storage-class-memory-learning-from-3d-nand Stand 18.01.2018

Abbildung 2.21.: Die veraltete 2D-Technologie wird von der zukunftsträchtigen 3D-Technologie im Rennen um verkaufte Bits überholt [ARI16]

Abbildung 2.22.: Übergang von der planaren 2D-NAND-Zelle zu einer 3D-NAND-Zelle[ARI16]

Speicherschichten, die übereinandergestapelt werden, erhöht [ARI16].

### 2.4.2. Grundprinzip

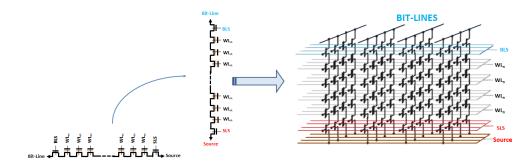

Bei der 3D-Architektur wurden die NAND-Strings (BLs) von einer horizontalen in eine vertikale Ebene gebracht. Dieser Vorgang wird auf Abbildung 2.23 verdeutlicht.

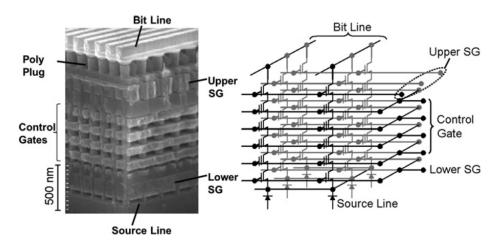

Daraus resultiert, dass der NAND-String nun in die vertikale "wächst" und somit die Erhöhung der Speicherdichte nicht mehr von der Verkleinerung der Feature Size (horizontale Ebene) abhängt. Zusätzlich wurde die Speicherdichte durch das Stapeln von Speicherschichten übereinander erhöht, wobei die Chipgrundfläche dabei konstant bleiben konnte. Auf Abbildung 2.24 ist die erste Umsetzung eines 3D-Speichers, die BiCS abgebildet. Auf der linken Seite sieht man den realen Speicher unter einem Elektronen-Mikroskop vergrößert und auf der rechten Seite die dazugehörige Schaltung. Wichtig zu erkennen ist hier, wie die vorher planaren BLs nun in die vertikale Ebene gedreht wurden. Das Grundprinzip ist weiter

$<sup>^{2}</sup>$ Quelle: Interne Präsentation von BMW

Abbildung 2.23.: Übergang des NAND-Strings von horizontaler Ebene in die Vertikale<sup>2</sup>

Abbildung 2.24.: BiCS-Zelle unter Rasterelektronenmikroskop und äquivalente Schaltung[ARI16]

nicht sehr verschieden von der 2D-Architektur, deswegen ist die konkrete Implementierung dieser Technik das große Forschungsthema. Einen großen Unterschied gibt es zur grundsätzlichen 2D-Flash-Zelle, zumindest bei den meisten Implementierungen von 3D. Während die 2D-Flash-Zelle ihre Ladung in einem Floating Gate abspeichert, wird die Ladung bei den meisten 3D-Implementierungen in sogenannten Charge Traps (CTs) abgespeichert. Diese Technologie ist nicht neu, trotzdem wurde sie bei den 2D-Flash-Speichern kaum verwendet. Beim CT werden die Ladungen nicht im Floating Gate gespeichtert, sondern es werden Elekronen in einer Schicht aus Siliciumnitrid "gefangen". Es gibt allerdings auch eine Implementierung, bei der noch ein Floating Gate verwendet wird. Im nächsten Unterkapitel gibt es dazu eine Übersicht [ARI16].

# 2.4.3. Übersicht Architekturen

Auf Abbildung 2.25 sind die vier wichtigsten Implementierungen des 3D-Ansatzes mit ihren verschiedenen Eigenschaften dargestellt. Schon beim alleinigen Betrachten der konkreten Architektur fällt auf, dass hier fundamentale Differenzen vorhanden sind. Die 3D-Architekturen unterscheiden sich viel gegenseitig, im Vergleich zu verschiedenen 2D-Implementierungen untereinander. Auffällig ist auch, dass nur eine der vier Technologien die FG-Zelle verwendet. Eine weitere Ungleichheit ist die Geometrie des NAND-Strings. Während zwei der Techno-

|                                      | TCAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P-BiCS                          | 3DFG                     | SMArT                                |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|--------------------------------------|

|                                      | The state of the s |                                 |                          |                                      |

| Marke                                | V-NAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BiCS Flash                      | 3D-NAND                  | 3D-NAND                              |